# **Correctness of Multi-Core Processors with Operating System Support**

#### **Dissertation**

zur Erlangung des Grades des Doktors der Ingenieurswissenschaften der Fakultät für Mathematik und Informatik an der Universität des Saarlandes

> eingereicht von Petro Lutsyk

Saarbrücken, Oktober 2018

Tag des Kolloquiums: 27. September 2018

Dekan: Prof. Dr. Sebastian Hack

Vorsitzender des Prüfungsausschusses: Prof. Dr. Verena Wolf

1. Berichterstatter: Prof. Dr. Wolfgang J. Paul

2. Berichterstatter: Dr. Silvia Melitta Müller

Akademischer Mitarbeiter: Dr. Jonas Oberhauser

#### Zusammenfassung

Im Zuge der Unterstützung von Hypervisoren verifizieren wir einen realistischen Pipeline-Multi-Core-Prozessor mit integriertem Mechanismus für die zweiphasige (verschachtelte) Adressübersetzung. Das verschachtelte Übersetzungsschema wird benötigt, damit Gäste des Hypervisors (typischerweise Betriebssysteme) ihre Programme im übersetzten Modus ausführen können. Wir betrachten das Setup, in dem die Betriebssysteme als Prozesse (im übersetzten Modus) des Hypervisors laufen, 'auf der bloßen Hardware', d.h. ohne Adressübersetzung.

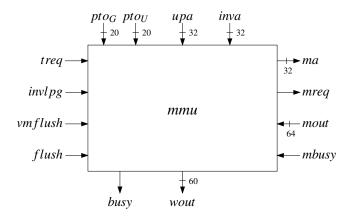

Die geschachtelte Übersetzung wird von der geschachtelten Memory Management Unit (MMU) durchgeführt, wobei beide Übersetzungsphasen in Hardware ausgeführt werden. Sowohl die Spezifikation als auch die Implementierung der geschachtelten MMU werden ausführlich dargestellt. Es wird bewiesen, dass die geschachtelte MMU eine allgemeinere Hilfsspezifikation, die die geschachtelte MMU vom Rest der Maschine isoliert, korrekt implementiert. Letzteres erlaubt es uns, die Argumente für die Korrektheit der MMU-Implementierung in jeder Maschine auf eine einfache Simulation zwischen zwei Softwaremodellen zu reduzieren.

Der Hauptbeitrag dieser Arbeit ist der vollständige Korrektheitsbeweis auf Papier für die Pipeline-Multi-Core-Implementierung des MIPS-86 ISA, der zur Unterstützung der verschachtelten Übersetzung zusätzlich erweitert wurde. Wie der Name schon vermuten lässt, kombiniert MIPS-86 den Befehlssatz von MIPS mit dem Speichermodell von x86. Zuerst betrachten wir diese erweiterte MIPS-86-Spezifikation in der sequentiellen Implementierung, die dazu dient, die Integration der verschachtelten MMUs in den MIPS-Prozessor zu demonstrieren und der Einfachheit halber auf einen einzelnen Prozessorkern beschränkt ist. Im Beweis unseres Hauptergebnisses — Korrektheit der Pipeline-Implementierung — verweisen wir auf den sequentiellen Fall, um die Korrektheit der MMU-Operation zu zeigen. Dies erlaubt uns, den Fokus auf die Probleme des Pipelinings der Maschine mit spekulativer Ausführung und Unterbrechungen zu verlagern, die bei vorhandener Adressübersetzung zu berücksichtigen sind.

#### **Abstract**

In the course of adding support for hypervisors, we verify a realistic pipelined multi-core processor with integrated mechanism for two-phase (nested) address translation. The nested translation scheme is required to allow guests of the hypervisor (typically operating systems) to execute their programs in translated mode. We consider the setup in which the operating systems are running as processes (in translated mode) of the hypervisor, running 'on the bare hardware', i.e., without address translation.

The nested translation is performed by the nested memory management unit (MMU), with both phases of translation performed in hardware. Both the specification and the implementation of the nested MMU are presented in full detail. The nested MMU is proven to correctly implement an auxiliary, more general specification which isolates the nested MMU from the rest of the machine. The latter allows us to reduce arguments on correctness of the MMU implementation in any machine to a simple simulation between a pair of software models.

The main contribution of this thesis is the complete paper and pencil correctness proof for the pipelined multi-core implementation of the MIPS-86 ISA, additionally extended to support the nested translation. As the name suggests, MIPS-86 combines the instruction set of MIPS with the memory model of x86. First, we consider this extended MIPS-86 specification in the sequential implementation, which serves to demonstrate integration of the nested MMUs into the MIPS processor and for simplicity is restricted to have a single processor core. In the proof of our main result — correctness of the pipelined implementation — we refer to the sequential case to show correctness of the MMU operation. This allows us to shift the focus towards the problems of pipelining the machine with speculative execution and interrupts, which are necessary to consider in the presence of address translation.

#### Acknowledgments

First and foremost, I would like to thank Prof. Dr. Wolfgang J. Paul for an opportunity to study computer architecture at his chair and write a doctoral thesis under his supervision. Starting from the very first lecture, about six years ago, it is hard to remember a meeting where he would not try to share some of his experience, no matter that was in a lecture hall, on a dance floor, or in his kitchen. I thank Prof. Paul for his catching enthusiasm, endless optimism and patience. Needless to mention that most of the mathematical culture necessary to write this dissertation I learned from him, both through lectures and private lessons.

Also, I want to thank my colleagues, ever working at the chair, for keeping a friendly and creative atmosphere. Especially, I want to thank my friend Dr. Jonas Oberhauser for being always ready to answer (many of) my questions and help with an advice, being a responsive room mate and a great friend. Also, I am grateful to Jonas for giving me a hard time in our scientific discussions, which after all only motivated me to keep learning.

Finally, I want to thank my family and friends, who kept me motivated to complete this dissertation. First, I thank my parents, who always believed in me and gave me a chance to travel to Germany and try myself here. Also, I am thankful to my brother and his family, who took care of me during my stay in Germany from the first day. Last but not least, I thank my first, and hopefully last, dancing partner for her support and patience during the whole time together.

### **Contents**

| In | trodu  | ction    |                                                        | 1  |

|----|--------|----------|--------------------------------------------------------|----|

| Pa | art I  | Single   | e-Core MIPS with Address Translation                   | 7  |

| 1  | Defi   | nitions  | and Notation                                           | 9  |

|    | 1.1    | Sets, S  | equences, and Records                                  | 9  |

|    | 1.2    |          | an Operators                                           | 10 |

|    | 1.3    | Binary   | and Two's Complement Numbers                           | 10 |

|    | 1.4    | Memo     | ry                                                     | 12 |

|    |        | 1.4.1    | Embedding                                              | 12 |

|    |        | 1.4.2    | Sequential Semantics                                   | 13 |

| 2  | Spec   | ificatio | n                                                      | 15 |

|    | 2.1    | Basic 1  | MIPS                                                   | 15 |

|    |        | 2.1.1    | Instruction Tables                                     | 15 |

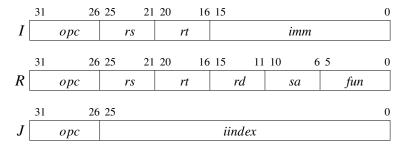

|    |        | 2.1.2    | Configuration and Instruction Fields                   | 17 |

|    |        | 2.1.3    | Instruction Decoding                                   | 19 |

|    |        | 2.1.4    | Processor-Local Operations                             | 20 |

|    |        | 2.1.5    | Memory Operations                                      | 25 |

|    | 2.2    | Summ     | ary                                                    | 26 |

|    |        | 2.2.1    | MIPS ISA                                               | 27 |

|    |        | 2.2.2    | Software Conditions                                    | 27 |

|    |        | 2.2.3    | Accesses of ISA                                        | 28 |

|    | 2.3    |          | pt Mechanism                                           | 30 |

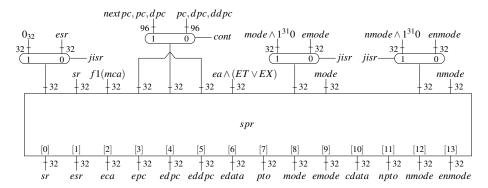

|    |        | 2.3.1    | Special Purpose Registers Revisited                    | 31 |

|    |        | 2.3.2    | Types of Interrupts                                    | 32 |

|    |        | 2.3.3    | MIPS ISA with Interrupts                               | 33 |

|    |        | 2.3.4    | Specification of Most Internal Interrupt Event Signals | 36 |

|    |        | 2.3.5    | Accesses of ISA Revisited                              | 37 |

|    | 2.4    |          | Level Address Translation                              | 37 |

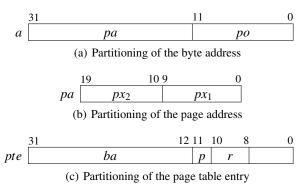

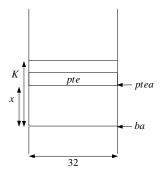

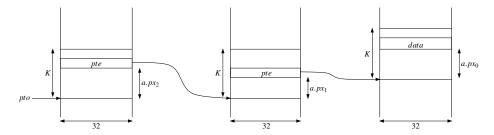

|    |        | 2.4.1    | Page Tables                                            | 37 |

|    |        | 2.4.2    | Walks and Translation Requests                         | 38 |

|    |        | 2.4.3    | MIPS ISA with Address Translation                      | 41 |

|    |        | 2.4.4    | TLB Steps                                              | 42 |

|    |        | 2.4.5    | Processor Core Steps                                   | 42 |

| Pa | ırt II | Nest     | ed Address Translation (NAT)                           | 47 |

| 3  | Intro  | oductio  | n and Specification                                    | 49 |

| -  | 3.1    |          | ization                                                | 49 |

|    |        | 3.1.1    | Translation Modes                                      | -  |

|    |        | 3.1.2    | Intercept Mechanism                                    |    |

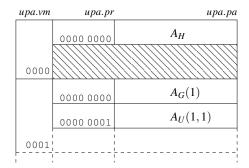

|    |        | 3.1.3    | Universal Addressing                                   |    |

|    |            |           |                                       | CONTENTS | VII   |

|----|------------|-----------|---------------------------------------|----------|-------|

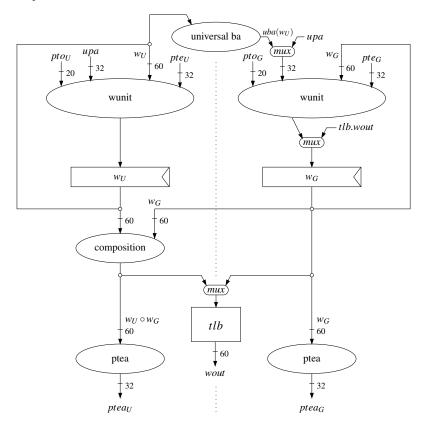

|    | 3.2        | Introdu   | ction to NAT                          |          |       |

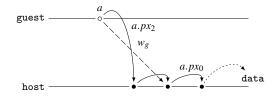

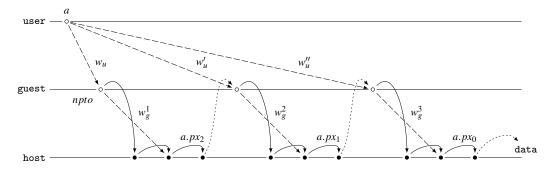

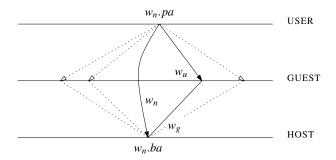

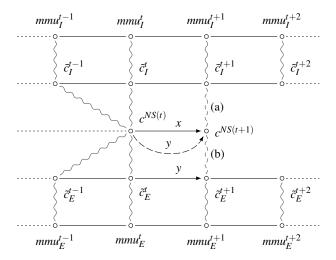

|    |            | 3.2.1     | Ideas behind Nested Translation       |          | . 53  |

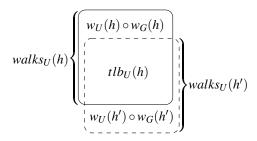

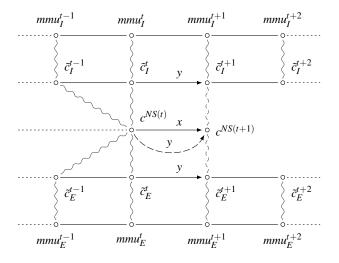

|    |            | 3.2.2     | Composition of Walks                  |          | . 56  |

|    |            | 3.2.3     | Decomposition of Nested Walks         |          | . 57  |

|    |            | 3.2.4     | Overloading Notation                  |          | . 58  |

|    | 3.3        | MIPS I    | SA with NAT                           |          | . 58  |

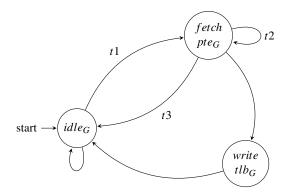

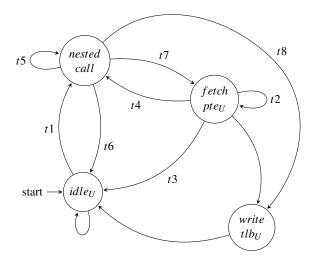

|    |            | 3.3.1     | TLB Component                         |          | . 59  |

|    |            | 3.3.2     | Translation Accesses                  |          | . 61  |

|    |            | 3.3.3     | Faults of NAT                         |          | . 62  |

|    |            | 3.3.4     | Processor Core                        |          | . 63  |

|    |            | 3.3.5     | Execution of Instructions             |          | . 65  |

|    |            | 3.3.6     | Overloading Instructions              |          |       |

|    |            | 3.3.7     | Interrupt Mechanism                   |          | . 67  |

|    | 3.4        |           | Ried Semantics                        |          |       |

|    | J.T        | 3.4.1     | General Semantics for TLB             |          |       |

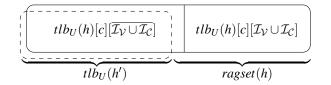

|    |            | 3.4.2     | Added, Dropped, and Ragged Walks      |          |       |

|    |            | 3.4.2     | TLB Equivalence                       |          |       |

|    |            | 3.4.3     | TEB Equivalence                       |          | . 70  |

| 4  | _          |           | tion of Nested MMU                    |          | 73    |

|    | 4.1        |           | gning TLB                             |          |       |

|    |            | 4.1.1     | Specification                         |          |       |

|    |            | 4.1.2     | Construction                          |          | . 76  |

|    | 4.2        | Redesig   | gning MMU                             |          | . 81  |

|    |            | 4.2.1     | Specification                         |          | . 81  |

|    |            | 4.2.2     | Construction                          |          | . 83  |

|    | 4.3        | Livenes   | 88                                    |          | . 93  |

|    |            | 4.3.1     | Simple Translations                   |          | . 94  |

|    |            | 4.3.2     | Nested Translations                   |          | . 98  |

| 5  | Cor        | rootnoss  | of NAT Implementation                 |          | 103   |

| 3  | 5.1        |           | ing MMU                               |          |       |

|    | 5.1        |           | e                                     |          |       |

|    | 3.2        |           | ness Statement                        |          |       |

|    |            | 5.2.1     | Stepping of TLB                       |          |       |

|    |            | 5.2.2     | Simulation of TLB                     |          |       |

|    | <b>~</b> 0 | 5.2.3     | Simulation Theorem                    |          |       |

|    | 5.3        |           | ping Formalism                        |          |       |

|    |            | 5.3.1     | Coverage of Hardware Walks            |          |       |

|    |            | 5.3.2     | Dropping Translations                 |          |       |

|    |            | 5.3.3     | Adding Translations                   |          |       |

|    | 5.4        |           | eness Proof                           |          |       |

|    |            | 5.4.1     | Void Queries                          |          |       |

|    |            | 5.4.2     | Translation Queries                   |          |       |

|    |            | 5.4.3     | Invalidation Queries                  |          | . 120 |

|    |            |           |                                       |          |       |

| Pa | art II     | I Sing    | le-Core MIPS with NAT                 |          | 123   |

| 6  | Som        | iential D | Processor with Nested MMUs            |          | 125   |

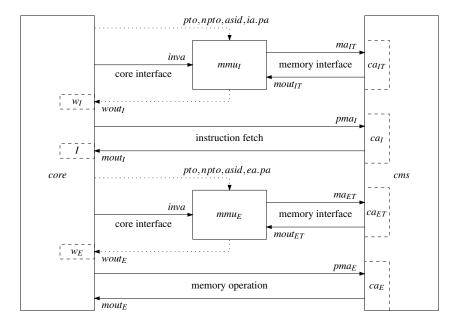

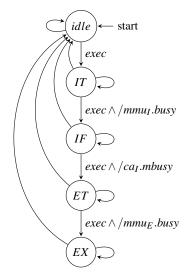

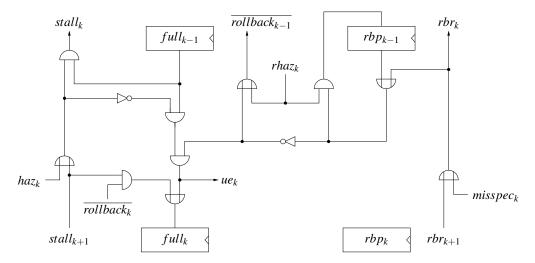

| U  | 6.1        |           | tial Processor                        |          |       |

|    |            | 6.1.1     | Control Logic                         |          |       |

|    |            | 6.1.2     | Collecting Interrupts                 |          |       |

|    |            | 6.1.3     | Implementation Registers              |          |       |

|    |            | 6.1.4     | Connecting Components                 |          |       |

|    |            | 6.1.5     | Execution Levels and Intercepts       |          |       |

|    | 6.2        |           | Memory System in Sequential Processor |          |       |

|    | 0.2        |           | Connections to Caches                 |          |       |

|    |            | 0.2.1     | Connections to Caches                 |          | . 134 |

| VIII | CONTENTS |

|------|----------|

|      |          |

|         |                    | 6.2.2                                                                                                                                                                                                                              | Stability of Inputs to Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                    | 6.2.3                                                                                                                                                                                                                              | Accesses of Hardware Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                    | 6.2.4                                                                                                                                                                                                                              | Relating Endings of Accesses with Hardware Control Signals 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 6.3                | Livene                                                                                                                                                                                                                             | ss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                    | 6.3.1                                                                                                                                                                                                                              | Liveness of Control States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                    | 6.3.2                                                                                                                                                                                                                              | Uniqueness of Finish Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7       | Com                | <b>4</b>                                                                                                                                                                                                                           | of Communical Invalencementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| /       | 7.1                |                                                                                                                                                                                                                                    | of Sequential Implementation145tness Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | /.1                | 7.1.1                                                                                                                                                                                                                              | Stepping of Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |                    | 7.1.2                                                                                                                                                                                                                              | Software Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                    | 7.1.3                                                                                                                                                                                                                              | Simulation Theorem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                    | 7.1.4                                                                                                                                                                                                                              | Stepping Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 7.2                |                                                                                                                                                                                                                                    | ping Formalism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | ,                  | 7.2.1                                                                                                                                                                                                                              | Scheduling Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                    | 7.2.2                                                                                                                                                                                                                              | Relating Global Steps with Scheduling Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 7.3                |                                                                                                                                                                                                                                    | tness Proof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                    | 7.3.1                                                                                                                                                                                                                              | Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |                    | 7.3.2                                                                                                                                                                                                                              | Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                    | 7.3.3                                                                                                                                                                                                                              | Implementation Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                    | 7.3.4                                                                                                                                                                                                                              | Maintaining Invariants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 7.4                | Correct                                                                                                                                                                                                                            | tness for TLBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                    | 7.4.1                                                                                                                                                                                                                              | Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                    | 7.4.2                                                                                                                                                                                                                              | Invalidation of TLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 7.5                | Verifvi                                                                                                                                                                                                                            | ng Guard Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1.5                |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 7.5                | 7.5.1                                                                                                                                                                                                                              | TLB Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 7.5                | •                                                                                                                                                                                                                                  | TLB Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 7.5                | 7.5.1                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ρź      |                    | 7.5.1<br>7.5.2                                                                                                                                                                                                                     | Processor Core Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pa      |                    | 7.5.1<br>7.5.2                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

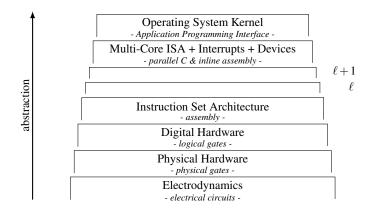

| Pa<br>8 | art IV<br>Pipe     | 7.5.1<br>7.5.2<br>V Mul                                                                                                                                                                                                            | ti-Core MIPS with NAT  rocessor with Nested MMUs  170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |