# Integrated Timing Verification for Distributed Embedded Real-Time Systems

# Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Fakultät für Mathematik und Informatik der Universität des Saarlandes von

# Pascal Montag

Saarbrücken 2018

Tag des Kolloqiums: 08.05.2018

Dekan: Prof. Dr. Sebastian Hack

Prüfungsausschuß:

Prof. Dr. Jan Reineke (Vorsitzender) Prof. Dr. Reinhard Wilhelm (Gutachter) Prof. Dr. Peter Marwedel (Gutachter)

Dr. Roland Leißa (Akademischer Mitarbeiter)

#### Abstract

More and more parts of our lives are controlled by software systems that are usually not recognised as such. This is due to the fact that they are embedded in non-computer systems, like washing machines or cars. A modern car, for example, is controlled by up to 80 electronic control units (ECU). Most of these ECUs do not just have to fulfil functional correctness requirements but also have to execute a control action within a given time bound. An airbag, for example, does not work correctly if it is triggered a single second too late. These so-called real-time properties have to be verified for safety-critical systems as well as for non-safety-critical real-time systems. The growing distribution of functions over several ECUs increases the amount of complex dependencies in the entire automotive system. Therefore, an integrated approach for timing verification on all development levels (System, ECU, Software, etc.) and in all development phases is necessary.

Today's most often used timing analysis method - the timing measurement of a system under test - is insufficient in many respects. First of all, it is very unlikely to find the actual worst-case response times this way. Furthermore, only the consequences of time consumption can thus be detected but not the potentially very complex causes for the consumption itself. The complexity of timing behaviour is one reason for the often late and thus expensive detection of timing problems in the development process.

In contrast to measurement with the mentioned drawbacks, there is the static timing verification which exists since many years and is applicable with commercial tools. This thesis studies the current problems of industrial applicability of the static timing analysis (effort, imprecision, over-estimation, etc.) and solves them by process integration and the development of new analysis methods.

In order to show the real benefit of the proposed methods, the approach will be demonstrated using an industrial example at every development stage.

## Kurzfassung

Unser tägliches Leben wird immer stärker von Software-Systemen durchdrungen, die oftmals nicht als solche wahrgenommen werden, da sie in Nicht-Computer-Systeme (Waschmaschinen, Autos, usw.) eingebettet sind. So arbeiten in einem aktuellen PKW bis zu 80 Steuergeräte.

Diese müssen in vielen Fällen nicht nur funktional korrekt arbeiten, sondern eine geforderte Berechnung auch innerhalb vorgegebener Zeitschranken ausführen. Ein Airbag erfüllt seine Aufgabe beispielsweise nicht, wenn er auch nur eine Sekunde zu spät ausgelöst wird. Die so genannten Echtzeiteigenschaften müssen für sicherheitskritische Anwendungen und soweit wie möglich auch für alle anderen Echtzeitsysteme, abgesichert werden.

Insbesondere sorgt die steigende Verteilung von Funktionen über mehrere Steuergeräte hinweg zunehmend für komplexe Abhängigkeiten im gesamten Fahrzeugsystem. Dies macht eine im Entwicklungsprozess und auf allen Abstraktionsebenen der Entwicklung (System, Steuergeräte, Software, usw.) durchgängige Methodik der Zeitverifikation notwendig.

Das heute übliche Verfahren der Zeitmessung von Systemen während der Testdurchführung ist in vielerlei Hinsicht ungenügend. Zum einen werden die tatsächlichen Grenzwerte nur mit sehr geringer Wahrscheinlichkeit erreicht. Zum anderen werden auf diese Weise nur die Auswirkungen von Zeitverbräuchen gemessen, nicht aber deren Ursachen analysiert, die möglicherweise sehr komplex sein können. Dies führt auch dazu, dass Probleme erst spät im Entwicklungsprozess erkannt und folglich nur mit hohen Kosten behoben werden können.

Neben den Zeitmessungen mit den genannten Nachteilen gibt es die statische Zeitverifikation. Diese ist bereits seit vielen Jahren bekannt und auch über entsprechende Werkzeuge einsetzbar. In der vorliegenden Dissertation werden die Probleme der industriellen Anwendbarkeit der statischen Zeitverifikation (Aufwand, Ungenauigkeit, Überschätzung, usw.) untersucht und mit einer durchgängigen Prozessintegration sowie der Entwicklung neuer Analyse-Methoden gelöst.

Der hier vorgestellte Ansatz wird deshalb in jedem Schritt mit einem Beispiel aus der Industrie dargestellt und geprüft.

## Acknowledgements

To my understanding wife Franziska, who went through this thesis' development with me and stood by my side during all the usual ups and downs in the process. To my sons Frederik and Jannik who taught me to appreciate the important things in life and to keep matters in perspective.

I also would like to express my special gratitude to my friend and supervisor Dr. Steffen Görzig for giving me the opportunity to work on static software analyses in such a great team and for supporting me all the way through. There are and were so many colleagues at Daimler that helped me grow personally and professionally that I cannot mention all of them. Most important to me are André Schmidt, Udo Gleich, Gordon Haak, Falk Vieweg, Gabriel Schwefer, Nader Alexan and Maciej Kicinski.

With great respect, I want to thank Prof. Reinhard Wilhelm for the fruitful discussions we had, for his patience and his insistence at times when I was about to give up.

I also want to thank Prof. Peter Marwedel for serving as referee on my thesis committee.

Last but not least, I want to thank my parents and my family for their continuous love and support.

# **Contents**

| 1 | Intr                                  | oduction                                  | 1  |  |

|---|---------------------------------------|-------------------------------------------|----|--|

|   | 1.1                                   | Motivation                                | 1  |  |

|   | 1.2                                   | Basics and Definitions                    | 3  |  |

|   | 1.3                                   | Structure and Overview                    | 4  |  |

| 2 | Embedded Real-Time System Development |                                           |    |  |

|   | 2.1                                   | Introduction and Definition               | 7  |  |

|   | 2.2                                   | Software Architecture Patterns            | 14 |  |

|   | 2.3                                   | Development Processes                     | 17 |  |

|   | 2.4                                   | Automotive Software Development           | 18 |  |

|   | 2.5                                   | Automotive Characteristics and Challenges | 22 |  |

|   | 2.6                                   | Conclusion                                | 25 |  |

| 3 | Challenges and Goals                  |                                           |    |  |

|   | 3.1                                   | Introduction and Definition               | 26 |  |

|   | 3.2                                   | Main Goals                                | 26 |  |

|   | 3.3                                   | Sub-Goals                                 | 27 |  |

|   | 3.4                                   | Challenges                                | 28 |  |

|   | 3.5                                   | Limitations                               | 28 |  |

|   | 3.6                                   | Conclusion                                | 29 |  |

| 4 | Aut                                   | omotive Case Study                        | 31 |  |

|   | 4.1                                   | Motivation for an Example                 | 31 |  |

|   | 4.2                                   | Finding Suitable Case Studies             | 31 |  |

|   | 4.3                                   | The Emergency Brake Assist (EBA)          | 31 |  |

|   | 4.4                                   | Conclusion                                | 35 |  |

| 5 | Stat | e of the Art in Timing Analysis                                      | 36  |

|---|------|----------------------------------------------------------------------|-----|

|   | 5.1  | Introduction and Definition                                          | 36  |

|   | 5.2  | WCET Analysis                                                        | 37  |

|   | 5.3  | WCRT Analyses                                                        | 41  |

|   | 5.4  | System Architecture Level Timing Analysis (SALT) $\ \ldots \ \ldots$ | 50  |

| 6 | TOA  | AD Approach Overview                                                 | 59  |

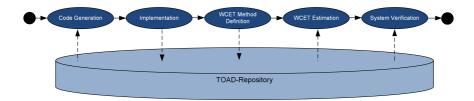

|   | 6.1  | TOAD - Timing Oriented Application Development $\dots$               | 59  |

|   | 6.2  | The TOAD Architecture (TOAD-A)                                       | 59  |

|   | 6.3  | The Tools and Methods (TOAD-T)                                       | 60  |

|   | 6.4  | The TOAD Development Process (TOAD-P) $\ \ldots \ \ldots$ .          | 61  |

| 7 | The  | TOAD Architecture (TOAD-A)                                           | 63  |

|   | 7.1  | Introduction and Definition                                          | 63  |

|   | 7.2  | Requirements                                                         | 63  |

|   | 7.3  | TOAD-A                                                               | 66  |

|   | 7.4  | Implementation of TOAD-A                                             | 74  |

|   | 7.5  | Developing TOAD-A Components                                         | 77  |

|   | 7.6  | Conclusion                                                           | 77  |

| 8 | Tool | s and Methods (TOAD-T)                                               | 78  |

|   | 8.1  | Introduction and Definition                                          | 78  |

|   | 8.2  | Development Tools                                                    | 78  |

|   | 8.3  | Integrated Timing Verification using Timed Automata                  | 82  |

|   | 8.4  | Static WCET Analysis                                                 | 88  |

|   | 8.5  | Variant-Aware WCET Analysis                                          | 96  |

|   | 8.6  | Static WCRT Analysis                                                 | 114 |

|   | 8.7  | Variant-Aware WCRT Analysis                                          | 122 |

|   | 8.8  | End-To-End Timing Analysis                                           | 124 |

|   | 8.9  | Optimisation                                                         | 125 |

|   | 8.10 |                                                                      | 126 |

| 9 | The  | TOAD Development Process (TOAD-P)                                    | 127 |

|     | 9.1    | Introduction and Definition                                     | 127 |

|-----|--------|-----------------------------------------------------------------|-----|

|     | 9.2    | On Existing Processes                                           | 128 |

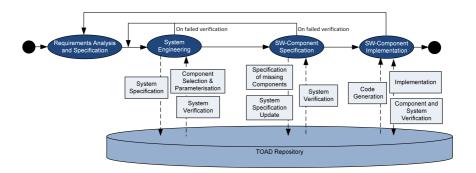

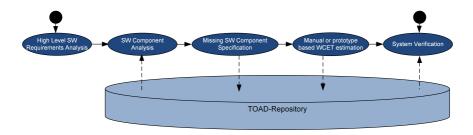

|     | 9.3    | The TOAD-P Process                                              | 128 |

|     | 9.4    | Supplier Management                                             | 133 |

|     | 9.5    | Conclusion                                                      | 134 |

| 10  | Resu   | ılts                                                            | 135 |

|     | 10.1   | Introduction                                                    | 135 |

|     | 10.2   | Evaluation                                                      | 135 |

|     | 10.3   | Technical Improvements                                          | 137 |

| 11  | Con    | clusion                                                         | 142 |

|     | 11.1   | Summary                                                         | 142 |

|     | 11.2   | Limitations of the Approach and Future Work $\ \ldots \ \ldots$ | 143 |

| Glo | ossary | <i>,</i>                                                        | 144 |

| Bil | bliogr | aphy                                                            | 146 |

|     |        |                                                                 |     |

# 1 Introduction

#### 1.1 Motivation

#### 1.1.1 Real-Time Requirements

The current decrease in deadly traffic accidents [Fed17] reflects the increasing number of active electronic safety systems in today's cars since they were first introduced with the ABS (antilock braking system).

Such systems do not only have to decide correctly whether or not to interfere in the braking process but have to do so within strictly defined time bounds. If the intervention is triggered too late, it may cost lives.

In general, adherence to real-time properties (cf. Section 2.1.2) is crucial when it comes to safety-critical systems. But they are also highly relevant to other automotive systems, like engine control, as injections have to be precisely timed with the engine's current rotation speed.

But there is also a tremendous amount of real-time systems outside of the automotive domain (e.g. multimedia, aerospace or medical devices), that can also benefit from the results of an integrated timing verification approach as introduced in this thesis.

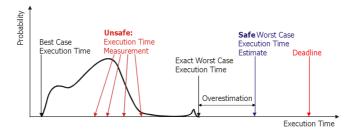

Figure 1.1: The difference between measurement and static analysis methods (adapted from [Abs17]).

#### 1.1.2 Timing Verification Instead of Measurement

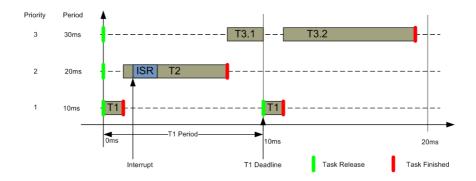

Today's most used timing analysis technique is measurement, which means that the response time of a system's tasks (cf. Section 5.3) are profiled while it is executed. However, due to the strong dependency on the execution state of the processor architecture, the same execution path may lead to different measurement results when executed twice. So you might miss the worst-case even if you have a full path coverage. In addition, due to most systems' complexity and the resulting high amount of possible execution paths, it is highly unlikely that the measurement of the response time actually hits the worst possible case (cf. Figure 1.1).

Therefore, a safety margin is added to the measured values. For example, the Daimler development standard allows a maximum of 80% CPU usage at the start of production. However, nobody can guarantee that the chosen safety margin is always sufficient. That is why almost all ECUs use a watchdog to dynamically supervise the correct task execution as well.

A watchdog however, can only reset or shut off a system and will thus reduce the availability of fail safe functions like the airbag. While the automotive industry seems to agree that this is acceptable for systems like the airbag as they are just systems that reduce the impact of an already occurred accident, it will not be sufficient for fail operational functions like autonomous driving.

Thus, the timing requirements of fail operational functions have to be formally verified in order to ensure safety. Additionally, timing verification is desirable for all safety functions as it will improve their availability.

But there are also economical benefits of static timing verification over measurement. As they deliver results early in the development the resulting changes can be made similarly early and thus, often with lower costs. Furthermore, static timing verification delivers detailed results and reasons for a particular timing behaviour, thus allowing for better decisions to optimise the timing behaviour.

# 1.1.3 Process Integration

One of the biggest challenges of static timing verification compared to measurement is that it requires detailed system and software architecture knowledge as well as some implementation knowledge for each and every software function in the system.

While a measurement only requires the execution of the system as part of a test, static timing verification requires the collection of precise function Worst-Case Execution Times (WCETs) as well as the correct calculation of task and system response times based on those WCETs. The simple problem in a distributed development environment is that there is usually not a single person that has such detailed and broad knowledge.

That is why this thesis claims that, in addition to technical improvements of the static timing verification methods, an integrated approach for timing verification is key to the industrial application of the technology. Such an integrated approach requires a common understanding of timing concepts and definitions. Beginning with the definition of timing properties of system and software architectures, covering development and analysis tool-chains and leading into a development process that defines the necessary tasks for different development roles (and typically people) in order to achieve a timing verification of the entire system.

#### 1.2 Basics and Definitions

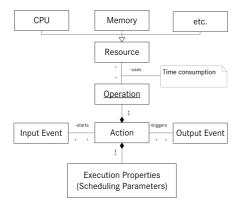

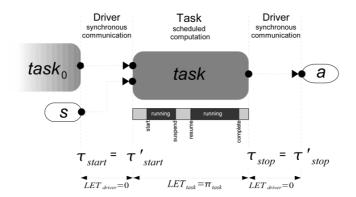

In electronic control units (and other electronic systems), time consumption results from hardware resource access operations. Such operations are triggered by an action (e.g. hardware trigger, code instruction, software function, operating system task) which itself is triggered by input events. In turn, actions result in output events as depicted in Figure 1.2.

Moreover, specific actions have specific execution properties. Tasks, for example, can be preemptive, have a periodicity and a worst-case response time (i.e. the worst-case time consumption between input event and output event).

The functional behaviour of an embedded real-time system can be depicted as an action or a sequence of actions that fulfil a high-level function. For the end user, the most relevant time span is the one between such a function's input event(s) (e.g. collision sensor impact) and the desired output event (e.g. airbag release). We call this time span the end-to-end response time (E2ERT).

But in order to understand this duration and its dynamics it is necessary to study the execution times of software functions as given by the worst-case execution time (WCET and the best and average case execution times (BCET and ACET) respectively (cf. Figure 1.1). Based on the

Figure 1.2: Real-time computational actions (adapted from [HGP<sup>+</sup>06])

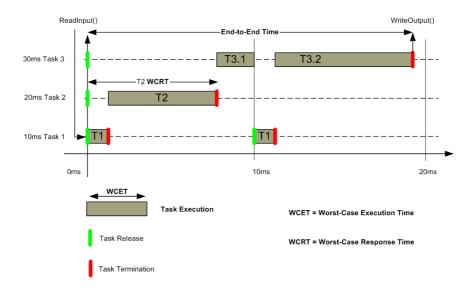

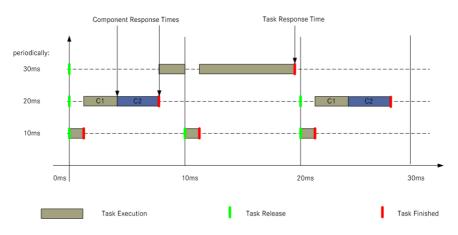

execution times, different levels of worst-case response times (WCRTs) can be estimated based on the execution properties of tasks, interrupts and communication messages (cf. Figure 1.3).

#### 1.3 Structure and Overview

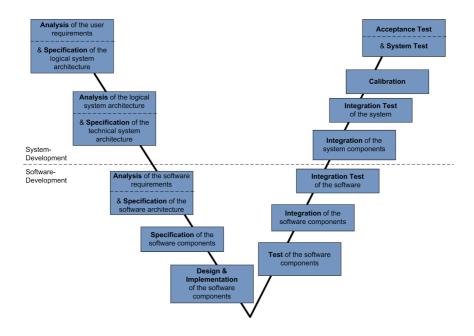

In the next chapter (Chapter 2), we are going to discuss the current state-of-the-art in embedded real-time system (ERTS) development. There, we will discuss different approaches to software architecture design in order to identify the necessary concepts for improving timing predictability. Furthermore, we will introduce system and software development processes in general and the automotive V-model in particular. The specific characteristics of the automotive domain will be in focus throughout this thesis and will be emphasised in this chapter to highlight the potential differences to other domains.

Based on the current development of real-time systems, Chapter 3 will introduce the current challenges as we see them. These goals will later be used to evaluate existing approaches and to compare them to the results of this thesis.

As a thesis with industrial background, we will use several real world examples from the Daimler development throughout this work. Moreover,

Figure 1.3: Schematic representation of timing analysis on task level.

in order to highlight the benefits of a continuous integration of the timing verification, we will use a central example, which will be introduced in Chapter 4.

In addition to the current state-of-the-art ERTS development, Chapter 5 introduces the state-of-the-art in timing analysis. Methods for the different levels of timing analysis (WCET, WCRT, E2E) will be introduced and discussed. This includes existing approaches for system-level timing definition and analysis, which we see as a key to an integrated approach.

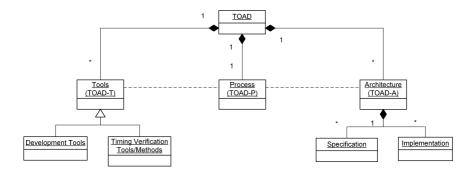

Chapter 6 introduces the TOAD (Timing-Oriented Application Development) approach that represents the proposed solution of this thesis. In this chapter we argue that an integrated approach requires a defined software architecture, methods and tools as well as a process to be applied in an industrial context.

The TOAD approach overview is followed by our proposal for a TOAD architecture (TOAD-A in Chapter 7) and the TOAD tool suite (TOAD-T in Chapter 8). The architecture and tools form the infrastructure for an

#### Introduction

integrated timing analysis that is used by the TOAD process (TOAD-P) which is described in Chapter 9.

Finally, we will sum up our results and compare them to existing approaches (cf. Chapter 10), followed by a discussion on the possible limitations of our approach (cf. Chapter 11).

# 2 Embedded Real-Time System Development

#### 2.1 Introduction and Definition

Embedded Real-Time Systems (ERTS) represent the majority of automotive electronic systems. Within a car, which represents the embedding system, they perform specific tasks like powertrain, brake or airbag control.

ERTSs are embedded systems which have to meet real-time requirements in order to operate correctly. Hence, they represent the target domain for an integrated timing verification.

A common understanding of embedded systems and real-time systems as well as their architectures is established in the following sections. Furthermore, as an integrated timing analysis includes the integration into a development process, the current system development in the automotive domain is discussed with regard to its special characteristics.

#### 2.1.1 Embedded Systems

An embedded system is a special-purpose hardware and software system, rather than a general-purpose computer (e.g. PC, smartphone). As its overall system design is focused on a small set of tasks such that these devices could be produced at a comparatively low cost in mass production. Embedded systems are usually not single devices but are rather built into an embedding system like a car, mobile phone or washing machine. Hence, people do not usually see the embedded systems, but rely on their correct behaviour. Only in error cases are people reminded of the complex electronic system which controls the device they use.

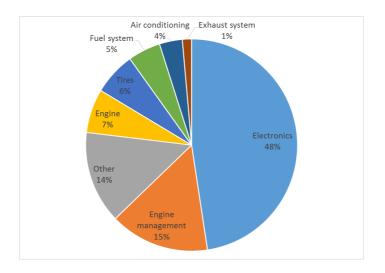

With the continuously increasing use of embedded systems that ease our lives and the simultaneous increase in the systems' complexity (e.g. by connecting single embedded systems to distributed systems), the amount of errors originating from embedded systems tends to increase. For example, the share of electronic-related car breakdowns from the overall breakdowns has increased from 35% in 2005 to 48% in 2015 (cf. Figure 2.1).

Figure 2.1: ADAC car breakdown statistic for Germany in 2015 [ADA16].

## 2.1.2 Real-Time Systems

Embedded systems use sensors to approximate the current state of the embedding system. Actions such as the acceleration towards a defined value are performed according to the current state (e.g. current speed) using actuators. As the state of the embedding system may change during the computation in the embedded system<sup>1</sup>, the computation time has a direct influence on the correctness of the result.

H. Kopetz defines a real-time system as follows [Kop97]:

A real-time (computer) system is a (computer) system in which the correctness of the system behaviour depends not only on the logical results of the computations, but also on the physical instant at which these results are produced.

The logical result of a computation originates from the functional requirements whereas the definition of the timing behaviour is a non-functional requirement that accompanies the functional requirements. A real-time

<sup>&</sup>lt;sup>1</sup>I.e. the state may change before an appropriate action is computed.

system is not necessarily a system that reacts fast, but rather a system that complies with the defined non-functional timing constraints.

The often referred to airbag system, for example, also has lower time bounds on some requirements. For example, the crash detection conditions have to be present for a defined duration before a crash can be safely detected as such. Thus, an early airbag release would result in a potential release without the actual occurrence of a crash. This is regarded as an even worse scenario than that of the occurrence of a crash and the non-release of the airbag. This is because for the former scenario, the early airbag release could very well be the cause of occurrence of a crash.

#### Hard and Soft Real-Time Systems

Soft real-time systems are real-time systems where only the quality of the result is affected by deadline misses. Hence, deadline violations do not necessarily lead to system failures but can be tolerated within defined ranges. An example for a soft real-time system is a video player. A limited amount of skipped video frames due to deadline violations can be tolerated.

Hard real-time systems however, do not allow the violation of deadlines. Thus, most of them have to perform exception handling operations like entering fail-safe states as soon as a single deadline is missed. A fail-safe state is, for example, the deactivation of the airbag functionality and an appropriate indication of the deactivation in the driver's instrument cluster.

Most automotive ECUs contain some kind of hard real-time functionality. Most of them do so because they have to communicate in a defined frequency which is usually standardised and thus, easy to implement. But roughly half of them also have more complex safety-relevant functionalities that are time-dependent in almost all cases.

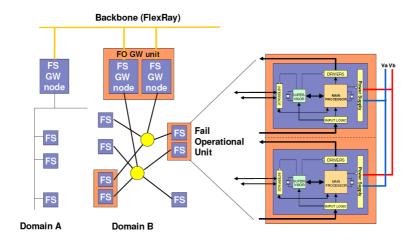

In opposite to fail-safe systems, there are fail-operational systems. Such systems have no fall-back fail-safe states for exception handling. Thus, systems like the Curiosity Mars-lander and upcoming autonomous cars make use of a redundant simplified functionality in case of exceptions like deadline misses. And those functionalities need guarantees on the defined time bounds.

Hence, the timing verification as it is presented in this thesis is crucial for fail-operational hard real-time systems. But it is also highly recommended

for all hard real-time systems and may even be helpful to ensure the quality and availability of soft real-time systems.

#### **Event and Time-Triggered Systems**

Every computer system is triggered by input events from external sensors and devices like buttons, radar sensors, clocks etc. The event of a clock tick is used for the so called time-triggered activations to start tasks or polled events periodically and thus, occur in a time deterministic manner. Event-triggered activations are therefore understood to be all non timetriggered activations. Such triggers are typically hardware interrupts that execute specific software-functions (i.e. interrupt service routines) in response to acyclic external events.

Most embedded systems today use event- and time-triggered functionalities together. The main part of the software functionality is often executed periodically in a time-triggered manner while concurrent functions (network communication, sensor information, etc.) result in interrupt events that deliver new input for the next main function cycle.

This mixture delivers the flexibility to react on non-deterministic inputs from the embedding system while the output events remain time deterministic.

The development of distributed time-triggered systems [Rus02] introduced globally-synchronised clocks (e.g. in the FlexRay network communication protocol [Fle07]) that allow time-determinism over several ECU-nodes with low latency as well as live-knowledge of the current E2E duration. This is very helpful for sensor-fusion functionalities, where all sensor inputs have to be synchronised in software. However, like watchdogs on ECU level, the knowledge of E2E violations can only result in an handling of such exceptions but cannot prevent them from happening. The latter is the intention of the proposed method in this thesis.

#### 2.1.3 Architectures

Different Architectures are used on different development levels in order to structure the design and distribution of development work. Here, we consider the system-, hardware- and software-level. On each one of these levels, architectures are used to define basic rules and structures of interaction for lower level subsystems. Thus, they also define the necessary

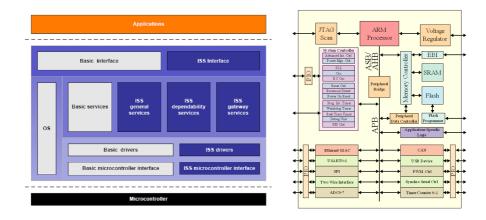

Figure 2.2: An example of a software architecture (left: architecture of Integrated Safety Systems (ISS), cf. [LHO<sup>+</sup>06]) and a hardware architecture (right: A system on-a-chip (SoC) for ARM).

collaboration of the teams developing these subsystems. And with regard to timing, it is the structure used to budget timing requirements and define scheduling rules.

The top level system in the automotive domain is the car itself, which consists of the physical system (e.g. mechanics and chemistry) and the embedded E/E system. The E/E system architecture (in the following only referred to as system architecture) defines the interplay of sensors, ECUs and actuators using communication connections.

# System Architecture

The Carnegie Mellon University (CMU) defines a system architecture in [Car07] as

a representation of a system in which there is a mapping of functionality onto hardware and software components, a mapping of the software architecture onto the hardware architecture, and human interaction with these components.

11

Figure 2.3: An example of an E/E system architecture (FS - Functional Software Component, GW - Gateway, cf. [LHO+06]).

For our use in the embedded real-time systems domain we adapt this definition to

a representation of a system in which there is a mapping of functionality onto hardware and software components, a mapping of the software architecture onto the hardware architecture, and external interfaces that allow the interaction with these components.

In the phase of hardware/software co-design, functional requirements are assigned to hardware or software elements. Performance, flexibility and changeability are major aspects in this early decision process. The highest performance is usually gained by hardware implementations while the highest flexibility is given by software implementations.

Depending on the chosen software architecture, a late (re-)deployment of software components is possible. Such a deployment is depicted in the system architecture in Figure 2.3.

Timing requirements are derived from the physical system and assigned to

the system architecture first. Hence, timing verification needs to start on the system level as well.

#### Hardware Architecture

A hardware architecture defines the electrical interfaces and the layout of the different hardware components (see an example in Figure 2.2 on the right hand side). The following levels of hardware architectures are relevant in this thesis:

- Network topology: The structural topology of sensors, actuators and ECUs as well as the communication channels between them.

- ECU architecture: The structural organisation of memories, interfaces and CPUs on a physical controller.

- Processor architecture: The logic design or implementation of a specific instruction set architecture.

Successful timing verification is based on predictable processor architectures. As the automotive industry has abandoned the idea of developing automotive specific processor architectures that could focus on predictability (presumably due to the high costs), the commercially available processor architectures with increasingly elaborate caches tend to become less predictable with regard to timing. Therefore, those processor architectures may be used, but the lack of predictability limits their full potential.

#### Software Architecture

Similar to predictable processor architectures, software architectures can be more or less predictable with regard to timing.

Clements et al. define a software architecture in [BCK03] as:

The set of structures needed to reason about the system, which comprises software elements, relations among them, and properties of both.

Hence, if we want to reason about the timing properties of a software architecture, we need to document structures, concepts and relationships that impact the timing behaviour. These are, for example, the scheduling strategy or component communication concepts.

#### 2.2 Software Architecture Patterns

In this section, a short overview on common software architectural styles (cf. [SG96, CKK02, BCK03]) is given and evaluated with regard to their timing predictability and general usage in embedded real-time development.

According to [CKK02], an architectural style

- Describes a class of architectures or significant architecture pieces.

- Is found repeatedly in practice.

- Is a coherent package of design decisions.

- Has known properties that permit reuse.

Some of the most common software architectural styles are introduced in the following sections.

#### 2.2.1 Event-Based Architectures

Event-based software architectures (also known as call and return architectures) are understood to be systems where functions are executed on demand instead of regularly in time. Representatives of this architectural style such as communicating processes or client server architectures are typically used to distribute systems on network nodes with a low computational overhead.

However, such systems tend to be unpredictable with regard to timing as there are no limits on the maximum frequency of possible requests (otherwise, one could choose a periodical execution accordingly). Hence, a timing verification is impossible until minimum distances between single event occurrences are defined (cf. Section 2.1.2).

#### 2.2.2 Data-Flow Architectures

A data-flow oriented execution, as it is used for example in pipes and filter architectures or batch sequential architectures, assumes the execution of processing components (e.g. filters) to be triggered by the availability of new input data. Although this concept seems to be most efficient, it becomes challenging if there are concurrent executions on a single CPU. In such cases, scheduling and synchronisation concepts are required in order to achieve consistency among dependent data streams. Similar to event-based

architectures, unlimited arrival rates of new data makes predictability impossible.

For example, an Emergency Brake Assist (EBA, cf. Section 4.3) that adjusts the target speed (which is controlled by a Cruise Controller) according to obstacles in front of the vehicle and triggers the brakes in emergency situations requires a higher priority than the cruise controller, due to its safety relevance.

Thus, the data-flow orientation is only meaningful when it is used on a single consistent data stream. In this case, a timing verification can be performed if the data arrival rate is limited. That is why data-flow architectures can often be found as part of more complex architectures (e.g. a single component of a component architecture follows the data-flow pattern).

#### 2.2.3 Blackboard Architectures

Blackboard architectures manage a central data-structure that contains the interface data of all processes and notifies processes of the arrival of new data according to predefined rules. Hence, the execution order depends not only on temporal distribution of input data, but also on potentially very complex rules.

The very high flexibility of this software architecture pattern results in a low and very difficult predictability.

## 2.2.4 Software Component Architectures

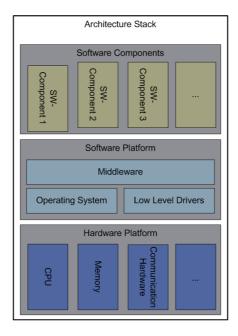

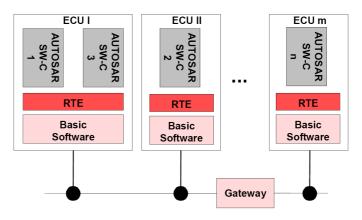

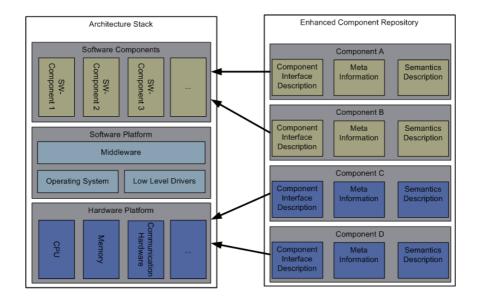

Software Component architectures (cf. Figure 2.4) focus on the definition of atomic units of execution, the components. These components can be triggered by data, events, requests or time. However, a time-deterministic software component architecture has to restrict the possible execution triggers, preferably to the periodic time trigger.

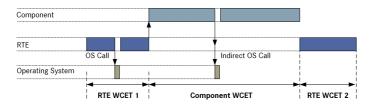

Software component architectures are usually built using a so-called runtime environment (RTE, also called middle-ware) which can be implemented as interpreter <sup>2</sup> or platform-dependent frameworks<sup>3</sup>. The use of interpreters usually leads to a lower performance than the use of platform-dependent frameworks. This is due to the fact that target specific hardware

<sup>&</sup>lt;sup>2</sup>In this case, the code-instructions are executed without a target specific compilation.

<sup>&</sup>lt;sup>3</sup>In this case, the components are compiled for the target hardware architecture.

Figure 2.4: A common component architecture.

features cannot be used for the component execution by interpreters. On the other hand, interpreters are more flexible in case the support of a wide range of different hardware is a requirement. As embedded systems typically have higher performance and power-consumption requirements than flexibility requirements, most embedded systems' component frameworks are platform-dependent.

Nevertheless, software component architectures allow for a certain degree of hardware-platform independence as the RTE is used to abstract from low-level drivers and services. Such components are only aware of their formal interfaces. There is no hard link to where data inputs or function calls originated from. This is done by the software-architect who defines the RTE-configuration.

The high level of standardisation within a component framework allows for an easy deployment of components in a pre-existing system architecture. But it also delivers a suitable infrastructure for system-level timing verification. The defined types and concepts allow the assignment of additional timing properties on an abstract level as well as the tracking of measurements and calculations on the implementation level.

## 2.3 Development Processes

A development process defines the activities, methods and procedures that are necessary for the development and verification of a (software) system.

Translation from [Bal98].

With regard to our timing verification approach, a domain independent process is required to define when and how different methods are to be applied to different work-products of a software development process (e.g. architecture, specification, code, etc.).

As explained earlier, we see one of the biggest challenges of timing verification in the fact that it cannot be assigned to a specific development step, but requires different actions on multiple development levels.

There are several standard process models for the software and system development (e.g. waterfall model, V-model, prototype model, etc.; cf. [Bal98]) whereas all of them describe the same three activities:

- 1. Requirements: The definition of the problem that the system/software(component) should solve.

- 2. Specification/Implementation: The structure of the solution to a given problem, which may deliver sub-problems that are defined as requirements on the next refinement-level.

- 3. Test/Verification: Ensuring, that the solution actually solves the problem. Or, on the top level, the validation of the initial problem description.

With regard to timing verification, functional problem definitions on the top level are extended by timing requirements (i.e. latest, earliest or never definitions). All functional requirements that require an action to take place need a mandatory timing requirement. While "earliest"-requirements can be assigned to specific components that potentially delay an action,

"latest"-requirements need to be budgeted on all contributing sub-problems in the specification/implementation phases.

Actually, this is one of the biggest challenges of the timing verification. At this point, estimations are required that may turn out to be wrong. Or they may even lead to unbalanced efforts between different parts of the solution (e.g. component A struggles to achieve a timing requirement while component B has an additional budget available). The result is that architects avoid budgeting and hope for a good outcome in the late verification phases. This, however, has the negative side-effect that without budget-requirements, every component and every ECU tries to be just "fast". In doing so, CPU resources are wasted and cannot be retrieved easily in late phases.

Further questions arise in the context of specific domains. The following analysis of the automotive software development process aims at the identification of the specific challenges in the automotive domain.

## 2.4 Automotive Software Development

The development of electric and electronic systems (E/E systems) in the automotive industry generally adopts the V-model for system development [SZ03] which distinguishes between system and hardware/software development (cf. Figure 2.5). This model specifically understands the hardware-and software-development to be parallel and rather independent activities. It is assumed that the system-level is able to decide which problem is to be solved in hardware and which in software. This is actually the case only to a certain extent. Because there are interdependencies between the two, especially when it comes to timing requirements, such system-level requirements cannot be assigned to either of them independently. This is an additional reason, why budgeting from the system to the implementation level is often not considered to be meaningful.

In the following sections, the phases of the V-model are discussed from an automotive OEM (Original Equipment Manufacturer) point of view.

# 2.4.1 Analysis of the user/system requirements and specification of the logical architecture

The system requirements are specified as system functions with their respective timing requirements.

Figure 2.5: The standard process of an automotive development according to [SZ03].

# 2.4.2 Analysis of the logical architecture and specification of the technical architecture

The specification of the logical and technical architecture are typically not separated. Hence, the OEM refines and assigns the functions to the ECU level in one step. By doing so, sensors, actuators and communication interfaces between the ECUs are defined. If timing requirements were not explicitly defined, the communication interface indirectly defines them. The update rate of messages is assumed to correlate with the update rate of the actual calculated values to be sent.

In most cases, the system development on ECU, sensor and actuator level is performed by one or more suppliers. Especially in the case of multiple suppliers, budgeting of timing requirements is necessary in order to avoid legal disputes. However, this is not always done due to the same reasons

19

as mentioned before.

The supplier defines the ECU architecture as well as the underlying hardware and software architecture(s). In doing so, he defines whether functions are implemented in hardware, software or a mix of both. Often, the supplier is additionally responsible for sensors or actuators and thus, for an end-to-end timing of a specific function.

Today, the choice of a specific hardware platform is mainly driven by the knowledge gained in previous projects, costs and market availability. As innovative projects lack the knowledge of previous projects, they sometimes require costly hardware changes towards the end of the project.

This may be prevented with a more structured estimation of the required and available resources.

# 2.4.3 Analysis of the software requirements and specification of the software architecture

As the functionality of the software and the deployment on different hardware nodes has been defined at the previous stage, the sub-functions are now structured into software components with their respective interfaces on different software layers (e.g. hardware abstraction, basic-services and application<sup>4</sup>).

While the distribution of functionality into different software components can be found in most projects, they often lack the definition of system states with different functional and timing behaviour (e.g. initialisation, normal mode, error mode, etc.)<sup>5</sup>. Also, the definition of sequences for time and safety critical functions is not available in most projects. And in the few projects that specify system states or sequences we can almost never find refined timing requirements or budgeting.

The issue at hand is that functional partitioning in the course of software design is a well understood discipline. The budgeting of timing requirements is not. The time partitioning has to follow the functional partitioning. But unlike the functional partitioning it is based on uncertain assumptions, that the software architect has to make. These assumptions are based on existing code, assumed effects of hardware changes and best guesses for new functions.

<sup>&</sup>lt;sup>4</sup> An application is understood as the set of system or project specific software functions.

<sup>&</sup>lt;sup>5</sup>The statements here are based on the author's experiences in software architecture reviews for more than 30 projects.

Based on today's timing specification gap, it is obvious that it will be difficult to perform a module-based timing verification in later phases of the development.

# 2.4.4 Specification, Design and Implementation of Software Components

On the level of software components, interfaces and functionalities are specified according to the software architecture, further refined and implemented (often in a single model or a C-file). In the majority of the cases where the specification of the software architecture already missed the refinement of timing requirements, the software component design can not make up for that. So, we have actually never seen a single project that defined execution time limits on the software component level.

Such time limits are necessary, for example, if a task is shared by components from different development parties. In such cases a simple ratio of allowed time consumption can already be helpful in early stages. If a 10ms task is allowed to execute components for 2.5ms (as deducted from the software architecture's other tasks and functions) a split of 1ms and 1.5ms can be estimated by the software architect, based on measurements and static timing verification for existing code or assumptions based on the functionality.

# 2.4.5 Integration, Test and Verification

Depending on the project, the integration, test and verification steps can be found on different levels. These are typically the software, the ECU and one or more system levels (with the car as the top level system). Testing and (timing) verification however, are not necessarily performed on all levels. As timing requirements are usually not refined or budgeted in today's system development, timing verification can usually be performed only on a higher level of abstraction. The first one being the task level of an integrated software system.

Due to the most often missing low level timing requirements, intrinsic timing requirements are used instead. These are given by the fact that the response times of tasks shall usually not exceed the task's period. And due to today's mostly used dynamic timing verification, an integrated ECU is usually the first level for timing verification. There are several issues that

arise here. On one hand, such a level of abstraction makes it difficult to achieve worst-case timing scenarios (due to the already high level of complexity) and makes debugging of potentially found timing violations more difficult. On the other hand, meeting task deadlines does not necessarily result in meeting end-to-end deadlines. This can only be achieved by a combined functional and temporal reasoning.

In conclusion, we can see that because of various reasons, timing requirements are not refined to a level where they can easily be handled or verified. This thesis targets the elimination of the identified root causes for that issue.

# 2.5 Automotive Characteristics and Challenges

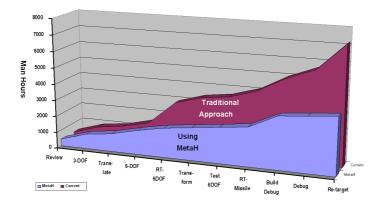

There are some specific characteristics of the automotive industry that make the timing verification issue more challenging. We have shown this in [MGL06b] for the static WCET verification with the tool aiT [Abs17].

#### 2.5.1 Scalability

A main characteristic is the complexity of today's automotive systems. Although the lines of code do not form the most meaningful metric for software complexity, it is clear that an increase from some 10,000 lines of code in the last century to around 100 million lines of code per car in 2017 implies an immense increase in software and systems complexity. Especially software-centric functions like multimedia, navigation or driver assistance require new forms of software architectures to cope with the increasing complexity.

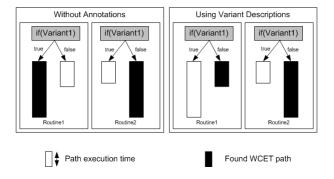

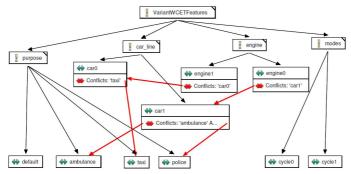

As the complexity tends to increase exponentially, so does the amount of system states and possible execution paths. Thus, timing verification has to rely on abstractions while remaining sound and precise, in order to scale with the complexity. For example, as most systems are not built from scratch, existing timing verification results (like loop-bounds or path constraint definitions) can be reused as well as the software components themselves. This, however, requires either abstract requirements on the possible execution contexts or a variant management detailed as detailed as the source code (e.g. parametrisable amount of gears for a gearbox software) which can be incorporated in the timing verification.

This requires in turn some level of standardisation on the software architecture and operating system level.

#### 2.5.2 Distributed Development

Distributed development in the automotive domain does not only imply multiple development locations but also different development companies, mainly suppliers and sub-suppliers. This mainly cost-driven automotive characteristic is a de-facto standard for every bigger OEM.

The integrated timing verification is affected by the following aspects of the distributed development:

- 1. Closed source development: The OEM has usually no access to the supplier's source code. Hence, suppliers have to deliver partial timing verification results that can be integrated similar to their components and systems.

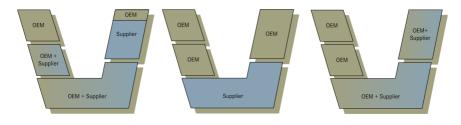

- 2. **Development scope:** There are systems that are completely developed by OEMs and there are systems that are completely developed by suppliers. And there are all shades of development scopes in between (cf. Figure 2.6). The partial timing verification results are required on every development level and need to be supplied from the OEM to the supplier in some special cases (e.g. OEM software component development and ECU integration on supplier side).

In general, code and verification results have to be reusable not only in different systems but also on different development levels with different levels of confidentiality.

Figure 2.6: Several possible distributed development approaches.

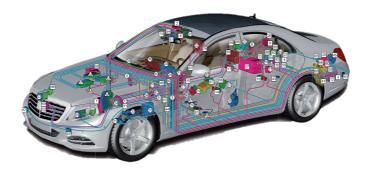

Figure 2.7: Distributed car functions that are activated at an imminent collision. Source: Daimler AG

# 2.5.3 Distributed Systems

As ECUs were developed similarly to mechanical components over a long period of time (i.e. independently by one supplier per ECU) the amount of ECUs has increased continuously to around 80. This high amount of separate controllers is not necessarily a functional requirement but more a reflection of historical mechanics centred development processes and responsibilities. Historically, there was no need for much communication between different development departments so that an ECU was typically developed by a single department. In turn, the ECU communication network can be seen as a reflection of the required communication between different OEM development departments.

However, the majority of today's innovative functions require increased communication in a network of different ECUs from different domains of the car (cf. Figure 2.7).

Therefore, it can be assumed, that the amount of distributed automotive systems will further increase in the future. The integrated timing verification approach has to support concepts for the timing analysis and verification of distributed systems. For safety-critical systems, the verification of worst-case communication delay guarantee is required. This requirement excludes non-time-deterministic distributed protocols, like TCP/IP, from the timing verification for safety-critical systems.

#### 2.5.4 Hardware Variants and Configurations

Most vehicles are highly customisable products. The richness of the resulting hardware variants is directly reflected by the software. As the resulting software parameter configurations result in constraints on the possible execution paths, they also vary in their possible worst-case execution time. On the one hand this leads to the necessity of static timing analysis as measurements cannot be carried out on all possible parameter combinations. Not to mention that correct guessing of worst-case variants is highly unlikely.

On the other hand, the timing verification of highly variant systems is currently not integrated into WCET analysis tools and requires formal variant descriptions which are not available for most projects.

#### 2.6 Conclusion

This chapter introduced embedded real-time systems and their development processes in the way they are understood as a basis for this thesis. Various concepts for embedded systems are furthermore classified with regard to their timing behaviour and execution concepts. The technical foundation is further given by definitions and examples of software-, hardware- and system-architectures. As a conclusion, all development levels impact the integrated timing verification approach and will be considered accordingly in this thesis.

Automotive characteristics and challenges are introduced in order to highlight some requirements that seem to be unknown to the timing verification community so far. The solution of these specific challenges will increase the acceptance of the static timing verification in the automotive domain and could thus lead to a wider range of application of the methodology.

# 3 Challenges and Goals

#### 3.1 Introduction and Definition

This chapter describes the identified challenges and defines resulting goals that are to be tackled in this thesis. These goals will be the basis for a later evaluation of the achievements of this thesis in comparison with existing approaches (cf. Section 5.4).

#### 3.2 Main Goals

The main goal of this thesis is to define a timing verification process that is industrially applicable. As stated in previous chapters (cf. Section 2.3 and 2.4) we see the overall integration of timing aspects into the entire development process as a key to that.

Furthermore, as all electric/electronic (EE) development projects try to find a balance between product quality (e.g. functionality, safety etc.), development time (i.e. short time to market) and costs (i.e. development and production costs), these aspects are similarly relevant for our integrated timing verification approach. We believe that underestimating time and costs often prevents otherwise helpful approaches from being industrially applied.

In addition to the goal of the general industrial applicability, the second main goal is the **consideration of automotive specific requirements** (cf. Section 2.5 and [MGL06b]). The consideration of specific automotive industry related challenges aims at an industrial domain that is currently not as concerned with safety as the aeronautics and space domains. But the future of the automotive domain will lift it to a similar safety level as there won't be even a human driver on board anymore. The specific requirements are going to be considered specifically in Chapter 4.

### 3.3 Sub-Goals

#### 3.3.1 Precision

As mentioned in Section 1.1.2 our goal is a timing verification that guarantees safe upper bounds for the timing estimations it produces. Furthermore, potential underestimations through wrong use of the analysis tools need to be indicated to the developer.

The method of choice for guaranteed upper time bounds is the static timing verification which faces the challenge of overestimation. So in order to be industrially applicable, our goal is to decrease the inherent overestimation. With regard to the specific automotive industry we see one major factor for an increased overestimation is the high amount of software and hardware variants. As the variants bear constraints on the possible execution paths, it is necessary to incorporate the potentially very complex constraint information which is often not explicitly given in the software.

Today's approaches to this problem are either to live with the overestimation or whenever that is not possible, to guess a worst-case variant and calculate its timing behaviour. The latter however, bears a high potential for underestimation. Hence, in order to achieve sound results, a variant-aware timing analysis is needed.

# 3.3.2 Generality and Flexibility

Using static analysis for timing verification is always limited by the supported hardware and software. And while our approach cannot support future hardware architectures out of the box, it can be generic and extendible to support these architectures.

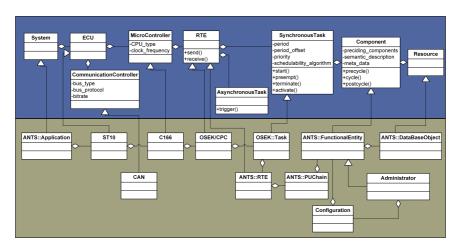

Software architectures and operating systems are less diverse in the automotive industry. For real-time systems, the vast majority uses AUTOSAR [AUT07] nowadays which follows a component architecture approach (cf. Section 2.2). In the rare cases that AUTOSAR is not used, either a variant of OSEK is used or no dedicated operating system (OS) is used at all. Hence, this thesis will focus on AUTOSAR/OSEK systems only.

# 3.3.3 Usability and Automation

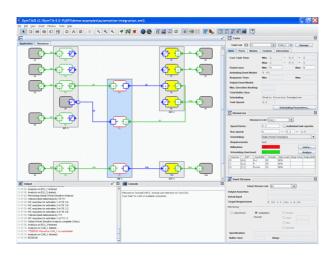

The academic background of automotive software developers is most often rather in mechanical engineering than in computer science. Thus, current methods of formal specification or verification are very difficult to be applied without sufficient abstraction and automation on the user interface level. The tooling also needs to be integrated into existing development tools in order to increase the acceptance rate (e.g. into software architecture development tools).

Finally, also the analysis computation duration itself needs to be in acceptable ranges (rather hours than days) so that the development process is not unnecessarily affected.

# 3.4 Challenges

#### 3.4.1 State Explosion

While the undecidability of the halting problem is a theoretical problem for the timing verification, the complexity of today's automotive embedded software is a practical one (cf. Section 2.5.1).

The analysis of a distributed real-time system in all its details (from source code to network communication) is not feasible today due to the state space explosion problem (cf. [MNL06]). The high amount of continuously changing input parameters that directly or indirectly influence the execution paths and thus, the timing behaviour, makes it nearly impossible to estimate safe time bounds in a reasonable time.

Hence, abstractions are necessary on many levels in order to reduce the number of relevant states considered in the timing verification. Every abstraction however, potentially reduces the precision of the analysis.

### 3.5 Limitations

#### 3.5.1 Hardware Correctness

The real-time behaviour of a software can only be computed for a given hardware which executes it. As hardware operates in the physical environment, there is always a certain probability for hardware faults and defects. This is the case no matter how safe and redundant a hardware architecture is defined.

The guaranteed bounds resulting from timing verification always assume non-faulty hardware. For example, the CPU clock rate has to be assumed to be exact or at least to stay within specified borders.

In contrast to influences from the physical environment to the hardware, the correctness of hardware logic itself can and should be verified in similar ways as software correctness.

#### 3.5.2 Software Correctness

Software and hardware logic follow semantics that are formally defined by the programming language (e.g. VHDL for hardware, ANSI C for software). External assumptions, like input contraints, are part of the specification. Thus, the semantics of the execution are well known, so that the correctness of the logic can be formally verified.

However, programming languages also bear undecidable properties as shown by Turing's proof on the halting problem in [Tur36].

The bottom line of the undecidability is that one cannot generally prove that an arbitrary algorithm will halt, though it is possible to prove it for specific subsets of algorithms.

Fortunately, most real world code can be verified to halt if it features specific properties. For example, fixed loop iteration bounds as well as prohibited use of recursions and function pointers can prevent straightforward termination issues. In addition, run-time error verification (e.g. pointer out of bounds write) and stack overflow protection prevent side effects that can lead to indirect termination issues.

### 3.6 Conclusion

This chapter discussed the main goals and challenges of this thesis. Those are:

- 1. The general **industrial applicability** goal of our approach requires an integration into current development processes and tools that are easy to use, precise and still able to guarantee time bounds.

- 2. The goal to tackle specific **automotive industry** related challenges requires the approach to take highly variant systems and their implications into consideration. Furthermore, the approach needs to be flexible and extendible in order to support the high amount of different hardware.

In addition to the aforementioned goals, the challenges of system complexity were discussed in this chapter.

# 4 Automotive Case Study

# 4.1 Motivation for an Example

PhD theses are meant to advance the current theoretical knowledge. Additionally showing the benefit of the gained knowledge in real world use is usually not a requirement. However, as this thesis focuses on the applicability of the developed approach, it is required to give a realistic proof of concept in order to explain the benefits for the industrial use-case.

# 4.2 Finding Suitable Case Studies

Not every example system is suitable to show what we want to achieve. As there are around 80 ECUs per car there will be some that do not exhibit the difficulties that most of the others do. Other ECUs may simplify the actual problems.

The following requirements can be derived from the main objectives of the TOAD approach (cf. Section 3.2).

- The system requirements have to include real-time properties.

- The system should be safety-relevant to necessitate a safe verification.

- The system should be non-trivial so that a manual verification is hardly possible.

- The system should cover the typical requirements of an automotive software system (mainly variability and distributed computing).

# 4.3 The Emergency Brake Assist (EBA)

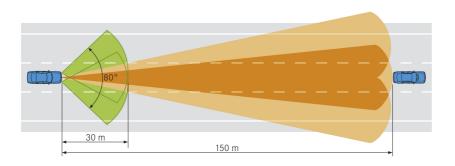

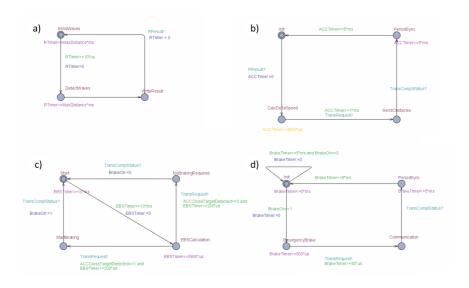

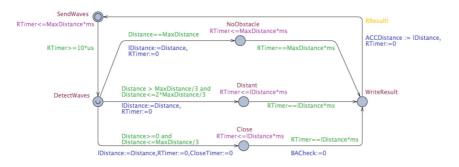

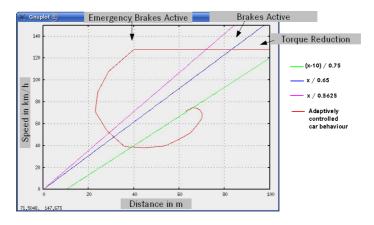

A system which fulfils the identified requirements is the Emergency Brake Assist (EBA, cf. Figure 4.1) which is similar to an Active Brake Assist (ABA) in the Mercedes Benz Actros truck (cf. [JS06]). Such a system can be seen as an advanced adaptive cruise control (CC) with the special ability to detect and react to the emergency situations of impending unavoidable collisions.

The EBA uses a radar to detect obstacles in front of the vehicle and adjusts the vehicle's speed accordingly.

Figure 4.1: Schematic diagram of the radar lobes of the EBA system.

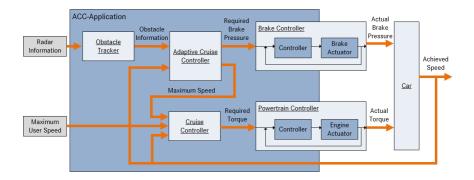

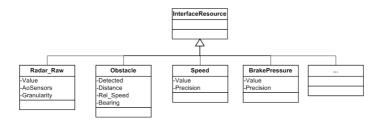

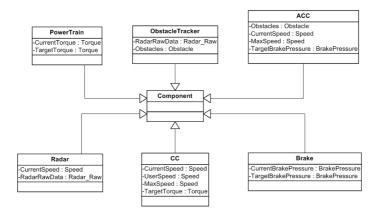

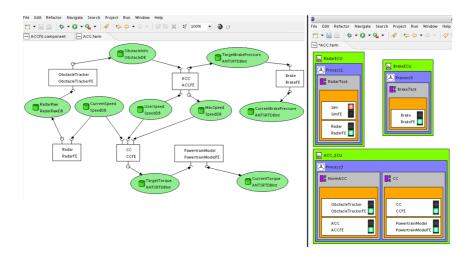

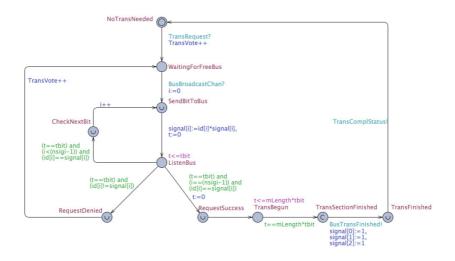

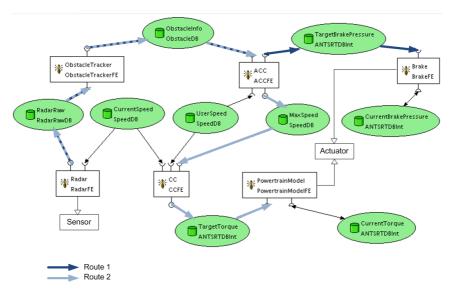

The logical architecture of an EBA system (cf. Figure 4.2) typically consists of six main components:

- 1. Radar The radar processes the information of the various radar sensors (e.g. two close range and three long range radars) and transforms it into corresponding distances for particular angles according to each sensor.

- 2. Obstacle Tracker The obstacle tracker uses the radar distance information to calculate the direction and relative speed of obstacles around the car (in our example the obstacles in front of the vehicle).

- 3. ACC The Adaptive Cruise Controller evaluates the current situation in order to adjust the maximum allowed speed accordingly. In emergency situations it triggers the brake by requesting up to 100% brake pressure.

- 4. CC The cruise controller takes the target speeds defined by the user and ACC and calculates the necessary torque on the powertrain (allows a limited deceleration compared to the brake).

- 5. Powertrain Controller The powertrain component adjusts the torque on the engine according to the CC and opens the clutch in emergency brake situations.

Figure 4.2: Schematic diagram of an ACC system with additional emergency brake functionality (EBA).

6. Brakes - The brakes translate the ACC's brake commands into brake actuator commands and executes them on the mechanics. For example, it contains the ABS functionality that prevents wheels from locking.

The potential deployment on different ECU nodes is mainly constrained by timing requirements. Thus, the radar preprocessing is either done directly within the radar sensor or on an ECU that is directly connected to the radar sensor. This saves bandwidth and thus reduces delays on the communication buses. Similarly, the powertrain and brakes software components are usually deployed on ECUs with direct access to the engine or the brakes respectively.

The obstacle tracker, CC and ACC software components on the other hand have rather limited data interfaces. The deployment decision can thus be made depending rather on the available CPU resources of the respective ECUs.

Today's adaptive cruise control systems are able to slow down the car in a specified range of deceleration by using the engine brake. Thus, no emergency braking is performed. This is mainly due to safety concerns as potentially faulty emergency brake interventions can lead to accidents instead of preventing them.

However, current developments in automotive system design are heading

towards a stronger interference in the cruising process as many accidents can only be prevented this way. An example of such a stronger interference is the Brake Assist PLUS in the actual Mercedes-Benz S-Class.

Such a system detects emergency situations with the radar sensors and increases the amount of brake pressure to the required level if needed as soon as the driver presses the brake pedal. Thus, the driver is still in charge of the trigger while the intensity of braking is controlled by the ECU.

The next step is a brake assist that is allowed to execute emergency braking independently of a driver's command. The Emergency Brake Assist (EBA) used for the demonstration of our methodologies is supposed to fulfil this requirement. Obviously, such an system requires a wide range of safety-specific development steps in addition to the timing verification.

Like most new automotive systems, the EBA is based on legacy software components and ECUs. In the case of the EBA these are the ACC ECU, which uses radar information to calculate obstacles and their distances, and the brake ECU, which calculates the necessary brake pressure depending on the current situation (e.g. different weight on each wheel) and a given deceleration value (by driver, ACC, etc.).

The new Emergency Brake Assist (EBA) represents an enhancement to the ACC controller as it adds an interface to the brake ECU. Hence, the existing brake ECU becomes part of the EBA system as it takes commands from the enhanced ACC component in addition to the driver's commands. The EBA example features the typical elements of an automotive software system as it is distributed (and potentially further distributable) and contains several variant parameters.

Parameters that are relevant for the system timing are ECU hardware parameters like the CPU type, the clock rate of this CPU, the memory layout etc. The communication bus is usually the same for all system variants. Recent developments using laser and camera sensors however, lead to additional variant parameters for the used communication buses (e.g. type, protocol, bit rate).

Additional system parameters are the car or truck type that is meant to use the system (e.g. different maximum speed and weight) as well as the amount of radar sensors to be processed, the resolution of the obstacle detection lobe, etc.

## 4.4 Conclusion

This chapter discussed the need for an automotive case study with a suitable example. Requirements for such an example are given and the Emergency Brake Assist (EBA) is introduced as one such system that fulfils those requirements. The complexity of the system (in the sense of timing verification) can be seen in the distribution over several hardware components and the potentially high amount of system variants.

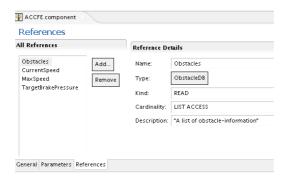

A detailed component specification for the EBA-system can be found in Chapter 8.

# 5 State of the Art in Timing Analysis

This chapter describes the current state-of-the-art by introduction and classification of timing analyses methods.

### 5.1 Introduction and Definition

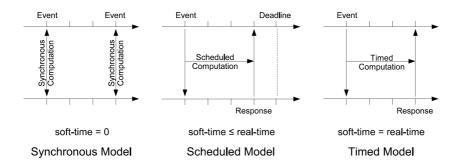

Following the development of embedded real-time systems, timing verification methods are performed on the different development levels. Different verification approaches are applied for system, task and implementation level where the lower levels verify the assumptions made by the specifications of the higher levels (e.g. message response time verifications verify system level communication protocol specifications).

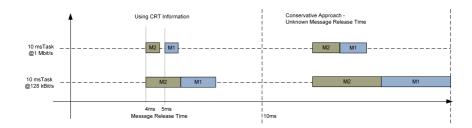

Starting on the system level, timing requirements are distributed using system architecture level models (c.f. Section 5.4). A verification on this level can already ensure, that the specified communication and ECU level computation times are consistent with the system requirements. The communication and ECU level computation times are then verified by WCRT analyses for the respective task or communication scheduling algorithm. The central input for the task response time is the WCET which represents an upper bound for the uninterrupted execution time of a machine code function on a particular hardware architecture.

WCET and WCRT analyses are well established methods in the timing analysis domain. Their current state and possible limitations will be discussed from Section 5.2.2 to 5.3. A less established timing verification level is the system architecture. While most developers assume that verified upper bounds on task and communication schedules sufficiently guarantee a system's timing behaviour, they miss the fact that safe bounds on end-to-end times require complete knowledge of all possible functional chains, synchronisation times between the tasks and communication messages, as well as all possible system states and system state transitions. Quite often error-, safe-, start- and shutdown states are not considered on end-to-end paths which results in unsafe system level timing although all single schedules are safe.

Hence, we distinguish three main classes of timing analyses: "WCET Analysis", "WCRT Analysis" and "System Architecture Level Timing Analysis".

# 5.2 WCET Analysis

The WCET represents an upper bound for the execution time of a specific software function, on a specific platform with a fixed set of parameters or external execution path constraints. A software function features varying worst-case execution times when executed on different execution hardware, but also for different sets of constraints (e.g. representing software or hardware variants).

Parameters or path constraints influencing the WCET are, for example, variant constraints (e.g. features a and b cannot be configured at the same time) or hardware constraints (e.g. the current project uses only one CAN (Controller Area Network [ISO93]) transceiver although the software supports up to four).

#### 5.2.1 Preliminaries

The WCET does not take into account that there are possible interruptions of the software function under analysis by tasks or interrupt service routines. The methods for the calculation of the WCET value can be static (without executing the software on the target hardware, cf. Section 5.2.2) or dynamic (by executing the software on the target hardware, cf. Section 5.2.3). There are also approaches that try to incorporate the benefits of both paradigms [BCP03] but remain elaborated dynamic WCET analysis methods.

# 5.2.2 Static Worst-Case Execution Time Analysis

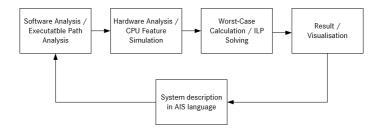

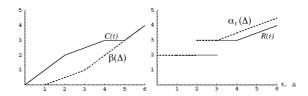

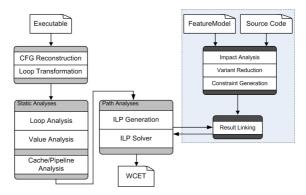

Time consumption occurs within information processing systems when the hardware executes machine-level commands and command sequences. That is why all static timing analyses (cf. Figure 5.1.) have models of specific hardware and use the software to be analysed as input.

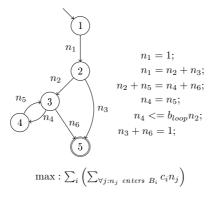

A most precise timing analysis would take only executable paths into consideration while neglecting infeasible ones. But as the question of whether a path can actually be reached or not can be reduced to the halting problem, this problem is also undecidable. Safe WCET values however, are

Figure 5.1: Workflow of a typical static WCET analysis exemplified on the tool aiT [Abs17].

not necessarily precise. Hence, tools like aiT (cf. [Abs17]) make use of the abstract interpretation (cf. [CC77]) which leads to safe but potentially overestimated sets of executable paths. Therefore, there will practically always be paths or loop iterations that cannot be executed but are part of the considered WCET path.

This overestimation cannot be determined as the actual WCET value is not known. However, an estimation can be performed by deriving the necessary input parameters for the calculated WCET path and executing such a worst-case scenario on the target hardware. That means, that by manually reviewing the calculated worst-case path, we can determine required inputs. Then we try to execute this path as closely as possible. Doing so might result in new insights on infeasible paths that can be modelled using specific constraint languages.

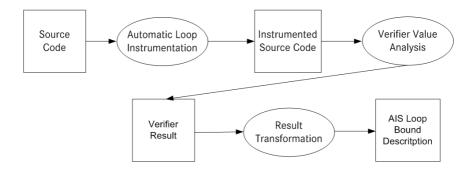

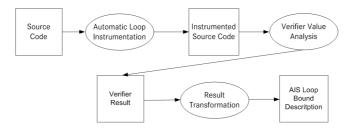

In order to determine a non-infinite WCET value, the upper bounds for the number of loop iterations and the number of possible recursion iterations have to be known at least. These values can be retrieved manually or partially automatically by static analyses.

But the calculation of a precise WCET estimate requires further restrictions of the control-flow than just the loop-bounds. It is necessary to know not only all possible value ranges of flow relevant variables but also the execution context in which specific values will occur.

The second step in the static timing analysis is the hardware and CPU feature analysis. There, safe overapproximations on the set of possible execution states are calculated for each program point in order to derive invariants for the estimation of a safe WCET with a low overestimation.

In the end, all feasible execution paths are weighted according to their execution time so that the calculation of a worst-case path can be performed. This is done by transforming the resulting control-flow graph into an optimisation problem. aiT uses the Implicit Path Enumeration (IPE) [LM99] to create an integer linear program (ILP) which can be solved with standard ILP solvers.

Successful case studies on static WCET verification have been applied to the automotive [MGL06b], space [HLS00, RSE<sup>+</sup>03] and avionics domains [The04, TSH<sup>+</sup>03]. Nevertheless, most of the case studies were performed on rather academic or small examples of code, whereas its application to highly parametric, complex industrial code has rarely been published so far.

### 5.2.3 Dynamic Worst-Case Execution Time Analysis/Profiling

### **Random Timing Measurement**

Nowadays, the most often used timing analysis method is the dynamic execution time analysis, which is also called program profiling. It is most often used as it is the cheapest form of timing analysis and it is rather intuitive for the developers. Profiling is often performed by measuring the timing behaviour during functional tests that have to be performed anyway.

The profiling in the embedded domain sometimes requires code changes (i.e. instrumentation) so that the trace start and end points of tasks or routines can be logged. Modern development hardware is able to measure the execution time without generating additional CPU overhead.

A drawback of dynamic timing analyses is that the execution of embedded systems usually requires the completely integrated system to be run and hence, the execution of all tasks and interrupts. So the developers will only get late feedback on the timing behaviour and often not on the level of their own implementation but rather on a generalised task-level. This circumstance prevents an early or even the general detection of inefficient coding.

But the main issue is that it is virtually impossible to find an actual WCET by profiling, as the amount of feasible software execution paths combined with the possible amount of hardware execution states is enormously higher than the time for testing permits to execute.

## **Search-Based Timing Measurement**

A more structured approach towards temporal behaviour testing is the evolutionary testing of real-time systems (cf. [Weg01, SBW01]). This approach is based on a structured selection of input parameters in order to maximise an optimisation function (also called fitness function). The fitness of a WCET analysis can be represented by the execution time which is to be maximised.

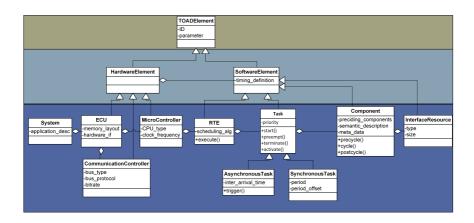

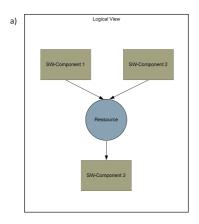

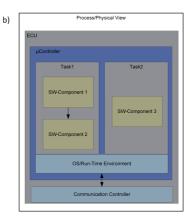

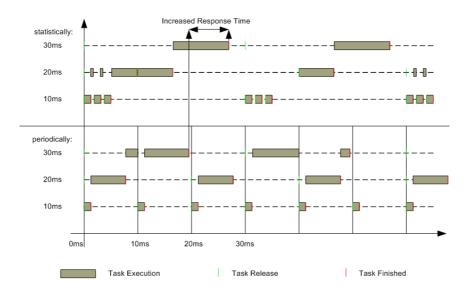

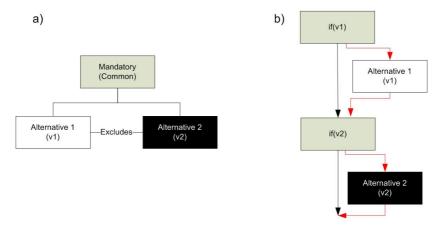

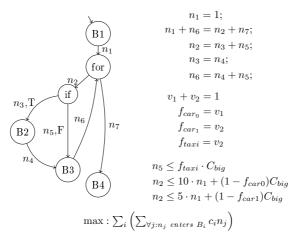

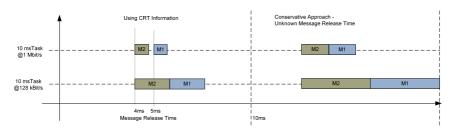

The selection of test parameter sets (individuals) can be performed by using ideas from the evolution theory [Dar59], in that parameter sets with high fitness values are selected (survive), recombined (parameter values are exchanged) and mutated (parameter values are randomly changed).