# **Timing Model Derivation**

Pipeline Analyzer Generation from Hardware Description Languages

## Dissertation

zur Erlangung des Grades des

Doktors der Ingenieurwissenschaften

der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

von **Diplom-Informatiker Markus Pister**

Saarbrücken Mai 2012

## Kolloquium

| Tag des Kolloquiums | Mittwoch, 19. September 2012        |

|---------------------|-------------------------------------|

| Dekan               | Prof. Dr. Mark Groves               |

| Prüfungsausschuss   |                                     |

| Vorsitzender        | Prof. Dr. Sebastian Hack            |

| Berichterstatter    | Prof. Dr. Dr. h.c. Reinhard Wilhelm |

|                     | Prof. DrIng. Wolfgang Kunz          |

| Akad. Mitarbeiter   | DrIng. Daniel Grund                 |

## **Impressum**

© 2012 Markus Pister

Herstellung und Verlag: Pirrot Verlag, Saarbrücken

ISBN: 978-3-937436-40-1

Das Werk ist urheberrechtlich geschützt. Jede Verwertung ist ohne Zustimmung des Verlages und des Autors unzulässig. Dies gilt insbesondere für die elektronische oder sonstige Vervielfältigung, Übersetzung, Verbreitung und öffentliche Zugänglichmachung.

Bibliografische Information der Deutschen Nationalbibliothek: Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

### **Abstract**

Safety-critical systems are forced to finish their execution within strict deadlines so that worst-case execution time (WCET) guarantees are a crucial part of their verification. Timing models of the analyzed hardware form the basis for static analysis-based approaches like the aiT WCET analyzer. Currently, timing models are hand-crafted based on frequently incorrect documentation causing the process to be error-prone and time-consuming.

This thesis bridges the gap between automatic hardware synthesis and WCET analysis development by introducing a process for the derivation of timing models from VHDL specifications. We propose a set of transformations and abstractions to reduce the hardware design's complexity enabling the generation of efficient and provably correct WCET analyzers. They employ an abstract interpretation-based simulation of program executions based on a defined abstract simulation semantics. We have defined workflow patterns showing how to gradually apply the derivation process to VHDL models, thereby removing timing-irrelevant constructs. Interval property checking is used to validate the transformations.

A further contribution of this thesis is the implementation of a tool set that realizes the introduced derivation process and shows its applicability to non-trivial industrial designs in experimental evaluations. Influences on design choices to the quality of the derived timing model are presented building an informal predictability notion for VHDL.

## Zusammenfassung

Sicherheits-kritische Systeme unterliegen oft der Einhaltung strikter Laufzeitschranken, weshalb zur Verifikation sichere Obergrenzen der Laufzeit im schlimmsten Fall (WCET) bestimmt werden. Zeitmodelle der analysierten Hardware sind hierbei die Grundlage für auf statischen Analysen basierende Verfahren. Aktuell werden solche Modelle händisch aus Handbüchern extrahiert, ein sehr zeitaufwändiger und fehleranfälliger Prozess.

Diese Arbeit schlägt eine Brücke zwischen automatischer Hardware-Synthese und der Entwicklung von WCET-Analysen durch die Einführung eines Ableitungsprozesses von Zeitmodellen aus VHDL-Spezifikationen. Transformationen und Abstraktionen werden zur Komplexitätsreduktion eingesetzt, um die Erzeugung von effizienten und beweisbar korrekten Analysatoren zu ermöglichen. Selbige bedienen sich abstrakter Interpretation von Programmausführungen basierend auf einer Simulations-Semantik. Definierte Arbeitsabläufe zeigen, wie man die Ableitung schrittweise auf VHDL-Modellen umsetzt und dadurch für das Zeitverhalten irrelevante Teile des Modells entfernt. Interval Property Checking gewährleistet hierbei, dass die Transformationen semantik-erhaltend sind.

Eine Tool-Implementierung realisiert den vorgestellen Ableitungsprozess und unterstreicht seine Anwendbarkeit auf komplexe industrielle Designs durch experimentelle Untersuchungen. Außerdem werden VHDL-Designentscheidungen hinsicht ihres Einflusses auf die Qualität des abgeleiteten Zeitmodells betrachtet.

## **Acknowledgments**

I want to express my gratitude to many people that have influenced this work in a variety of ways. First, many thanks go to *Prof. Reinhard Wilhelm* not only for allowing me to scientifically address this challenging topic. But also because I have learned a lot due to his ability to steer people into the right direction while still fostering their personal development by very free working conditions.

I am also very grateful to *Prof. Wolfgang Kunz* for his willingness to judge my thesis and his motivating interest in my work, in general. *Prof. Sebastian Hack* and *Dr. Daniel Grund* are the remaining members of my thesis jury, so I thank both for their commitment, as well.

Reinhold Heckmann, Daniel Kästner, Philipp Lucas, Stephan Thesing and Markus Wedler all have proof-red the thesis at hand and provided many excellent comments. I am indebted to them for this.

Thanks go to various (both current and former) colleagues at *AbsInt GmbH* and the *Compiler Design Group* at Saarland University. I enjoyed many hilarious (coffee) breaks with them over the last couple of years.

Although he has already been covered by the credits above, I want to point out my special thanks to my long-lasting colleague *Marc Schlickling*. We are cooperating since the early phases of our studies and have jointly developed large parts of the VHDL Derivation Tool Set. His ability to quickly find conceptual corner cases was a great help to me and I appreciate him a lot as my office roommate and friend.

During my research, I was (at least partly) funded by different European research projects *AVACS*, *ES\_PASS* and *Verisoft XT*, so I want to thank for these investments in my work.

Last but not least I want to thank my parents, *Christel* and *Gerhard*, and my love *Katharina* for their support in all phases of my life.

# **Contents**

| ı | Intro | oauctic | )N                                       | ı  |

|---|-------|---------|------------------------------------------|----|

|   | 1.1   | Embe    | dded Systems                             | 2  |

|   | 1.2   | Timin   | g Analysis of Embedded Systems           | 2  |

|   |       | 1.2.1   | The Timing Problem                       | 3  |

|   |       | 1.2.2   | WCET Analysis by Abstract Interpretation | 4  |

|   | 1.3   | Derivi  | ing Timing Models                        | 6  |

|   | 1.4   | Contr   | ibutions                                 | 7  |

|   |       | 1.4.1   | Timing Model Derivation                  | 8  |

|   |       | 1.4.2   | Simulation Semantics                     | 11 |

|   |       | 1.4.3   | Timing Model Validation                  | 11 |

|   |       | 1.4.4   | VHDL Predictability                      | 12 |

|   |       | 1.4.5   | VHDL Derivation Tool Set                 | 12 |

|   |       | 1.4.6   | Experimental Results                     | 14 |

|   | 1.5   | Thesis  | Outline                                  | 15 |

| 2 | Rela | ated Wo | ork                                   | 17 |

|---|------|---------|---------------------------------------|----|

|   | 2.1  | Worst-  | -Case Execution Time Computation      | 18 |

|   |      | 2.1.1   | Static Methods                        | 18 |

|   |      | 2.1.2   | Dynamic Methods                       | 22 |

|   |      | 2.1.3   | Hybrid Methods                        | 23 |

|   | 2.2  | Analy   | sis of Formal Hardware Specifications | 24 |

|   |      | 2.2.1   | Functional Verification               | 24 |

|   | 2.3  | Hardv   | ware Simulation                       | 26 |

|   |      | 2.3.1   | GHDL                                  | 26 |

|   |      | 2.3.2   | ModelSim                              | 27 |

|   |      | 2.3.3   | Summary                               | 27 |

| 3 | Eml  | bedded  | I Systems                             | 29 |

|   | 3.1  | Overv   | riew                                  | 30 |

|   |      | 3.1.1   | Characteristics                       | 31 |

|   |      | 3.1.2   | Real-Time Systems                     | 34 |

|   | 3.2  | Applie  | cation Areas                          | 36 |

|   |      | 3.2.1   | Automotive Electronics                | 36 |

|   |      | 3.2.2   | Aviation                              | 37 |

|   |      | 3.2.3   | Railway Electronics                   | 37 |

|   |      | 3.2.4   | Telecommunication                     | 38 |

|   |      | 3.2.5   | Medical Engineering                   | 38 |

|   |      | 3.2.6   | Military Applications                 | 39 |

|   |      | 3.2.7   | Authentication Systems                | 40 |

|   |      | 3.2.8   | Consumer Electronics                  | 40 |

|   |      | 3.2.9   | Fabrication Equipment                 | 40 |

|   |      | 3.2.10  |                                       | 41 |

|   | 3.3  |         | tectures                              | 41 |

|   |      | 3.3.1   | Overview                              | 41 |

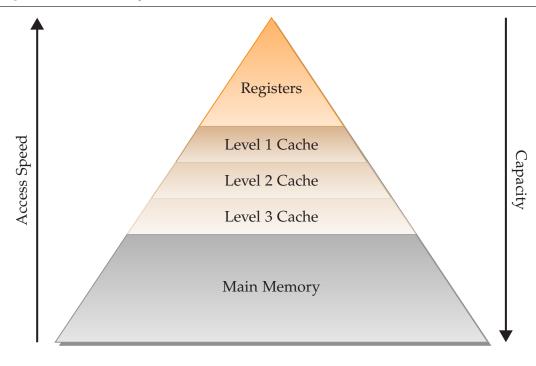

|   |      | 3.3.2   | Memory Hierarchies                    | 45 |

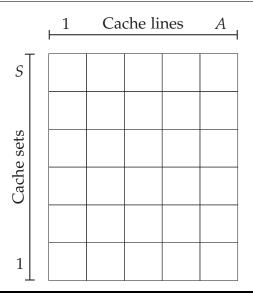

|   |      | 3.3.3   | Caches                                | 46 |

|   |      | 3.3.4   | Memory                                | 50 |

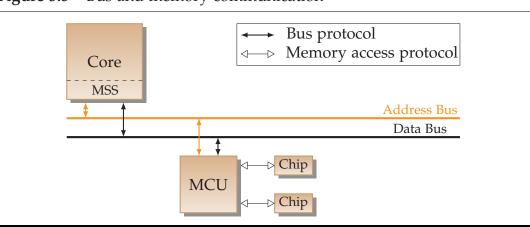

|   |      | 3.3.5   | Buses                                 | 52 |

|   |      | 3.3.6   | Peripheral Devices                    | 53 |

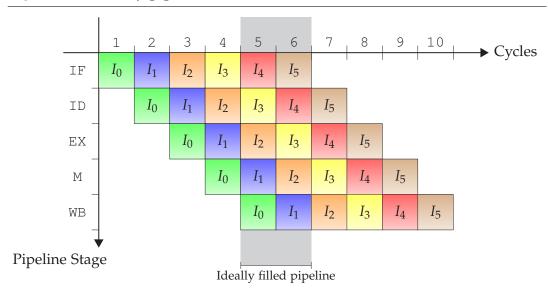

|   | 3.4  | Proces  | ssor Pipelines                        | 53 |

|   |      | 3.4.1   | Overview                              | 53 |

|   |      | 3.4.2   | Pipeline Hazards                      | 55 |

|   |      | 3.4.3   | Performance Improving Features        | 57 |

|   | 3.5  | Summ    | narv                                  | 62 |

| 4 |     | ing Analysis of Embedded Systems           | 63  |

|---|-----|--------------------------------------------|-----|

|   | 4.1 | Overview                                   | 64  |

|   | 4.2 | Classification of Approaches               | 65  |

|   |     | 4.2.1 Static Methods                       | 66  |

|   |     | 4.2.2 Dynamic Methods                      | 67  |

|   | 4.3 | aiT Worst-Case Execution Time Framework    | 68  |

|   |     | 4.3.1 Overview                             | 68  |

|   |     | 4.3.2 Decoding Phase                       | 70  |

|   |     | 4.3.3 Micro-architectural Analysis Phase   | 75  |

|   |     | 4.3.4 Path Analysis Phase                  | 83  |

|   |     | 4.3.5 Visualization Phase                  | 86  |

|   |     | 4.3.6 User Annotations                     | 87  |

|   | 4.4 | Summary                                    | 88  |

| 5 | For | mal Hardware Specifications and Synthesis  | 89  |

|   | 5.1 | Overview                                   | 90  |

|   | 5.2 | VHDL                                       | 92  |

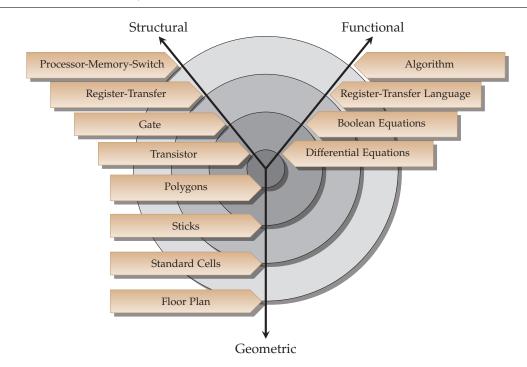

|   |     | 5.2.1 Domains and Abstraction Levels       | 93  |

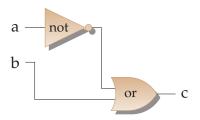

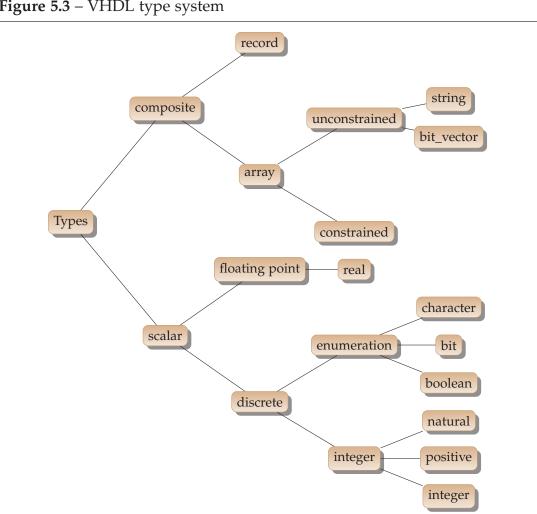

|   |     | 5.2.2 Basic Language Constructs            | 95  |

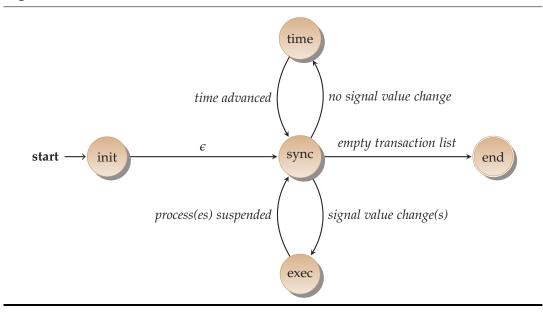

|   |     | 5.2.3 Semantics                            | 101 |

|   |     | 5.2.4 Analysis, Elaboration and Simulation | 104 |

|   | 5.3 | Hardware Synthesis                         | 106 |

|   | 5.4 | Summary                                    | 108 |

| 6 | Der | ivation of Timing Models                   | 109 |

|   | 6.1 | Overview                                   | 110 |

|   | 6.2 | Timing Models                              | 111 |

|   |     | 6.2.1 Nondeterminism                       | 112 |

|   |     | 6.2.2 Timing Anomalies                     | 115 |

|   | 6.3 | Analyzing VHDL Models                      | 116 |

|   |     | 6.3.1 Mapping VHDL to CRL                  | 117 |

|   |     | 6.3.2 Semantic Level Reduction             | 118 |

|   |     | 6.3.3 Abstract Interpretation of VHDL      | 119 |

|   | 6.4 | Semi-Automated Timing Model Derivation     | 120 |

|   |     | 6.4.1 Model Preprocessing                  | 121 |

|   |     | 6.4.2 Model Abstractions                   | 125 |

|   |     | 6.4.3 Model Transformations                | 128 |

|   | 6.5 | Timing Model Derivation Workflow           | 131 |

|   |     | 6.5.1 Application of Model Preprocessing   | 132 |

|   |     | 6.5.2 Application of Model Abstractions    | 136 |

#### Contents

|   |      | 6.5.3 Derivation Step Categorization | 141 |

|---|------|--------------------------------------|-----|

|   | 6.6  | 1 0                                  | 143 |

|   | 6.7  | Summary                              | 144 |

| 7 | Pipe | eline Analyzer Generation 1          | 47  |

|   | 7.1  | Overview                             | 148 |

|   | 7.2  | Concrete Simulation                  | 148 |

|   |      | 7.2.1 Operational Semantics          | 149 |

|   |      | 7.2.2 Activation Sequences           | 154 |

|   |      |                                      | 155 |

|   | 7.3  | Abstract Simulation                  | 155 |

|   |      | 7.3.1 Simulation Trees               | 156 |

|   |      | 7.3.2 Abstract Operational Semantics | 159 |

|   |      | 7.3.3 Correctness and Soundness      | 165 |

|   | 7.4  | Summary                              | 166 |

| 8 | Tim  | ing Model Validation 1               | 67  |

|   | 8.1  |                                      | 168 |

|   | 8.2  | Legacy Validation Approaches         | 168 |

|   |      |                                      | 169 |

|   |      | •                                    | 170 |

|   | 8.3  | •                                    | 171 |

|   |      |                                      | 172 |

|   |      |                                      | 173 |

|   |      |                                      | 174 |

|   | 8.4  |                                      | 175 |

|   |      |                                      | 178 |

|   | 8.5  |                                      | 179 |

|   | 8.6  | Future Work                          | 180 |

| 9 | Tim  | ing Predictability 1                 | 83  |

|   | 9.1  | •                                    | 184 |

|   | 9.2  |                                      | 186 |

|   |      |                                      | 187 |

|   |      | 1                                    | 188 |

|   |      |                                      | 189 |

|   |      |                                      | 190 |

|   |      | 9                                    | 192 |

|   |      | 1                                    | 192 |

|   |      |                                      | 194 |

|     | 9.3  | Timing Impact of VHDL Constructs                | 195 |

|-----|------|-------------------------------------------------|-----|

|     |      | 9.3.1 Predictability Enhancing Design Decisions | 196 |

|     |      | 9.3.2 Predictability Degrading Design Choices   | 198 |

|     | 9.4  | Summary                                         | 200 |

| 10  | VHD  | L Derivation Tool Set Implementation            | 203 |

| . • |      | Structure of the VHDL Derivation Tool Set       | 204 |

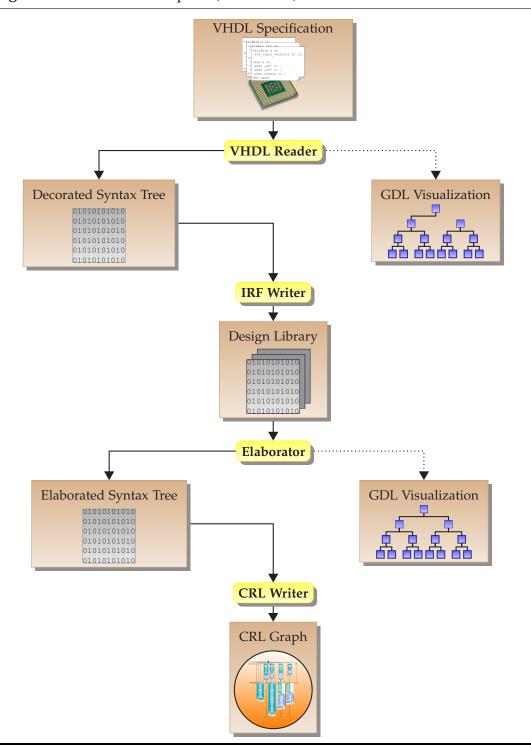

|     |      | VHDL Compiler                                   | 206 |

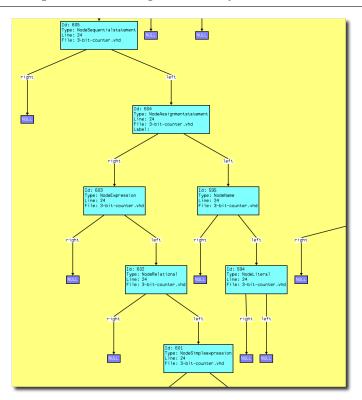

|     |      | 10.2.1 Analysis                                 | 206 |

|     |      | 10.2.2 IRF Writer                               | 208 |

|     |      | 10.2.3 Elaboration                              | 211 |

|     |      | 10.2.4 CRL Writer                               | 212 |

|     |      | 10.2.5 Usage                                    | 216 |

|     |      | 10.2.6 Complexity                               | 217 |

|     | 10.3 | Static Analyzers                                | 218 |

|     |      | Model Transformers                              | 218 |

|     |      | 10.4.1 Timing Dead Code Eliminator              | 219 |

|     |      | 10.4.2 Domain Abstractor                        | 222 |

|     |      | 10.4.3 Process Replacer                         | 225 |

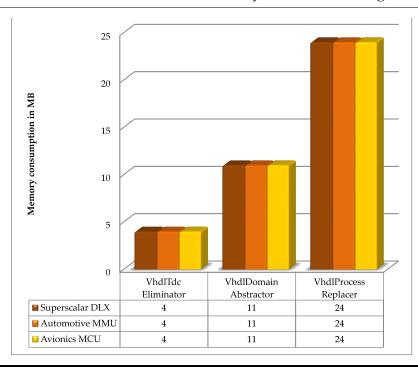

|     |      | 10.4.4 Complexity                               | 226 |

|     |      | 10.4.5 Usage                                    | 226 |

|     | 10.5 | Generators                                      | 227 |

|     |      | 10.5.1 Pipeline Analyzer Generator              | 227 |

|     |      | 10.5.2 Abstract VHDL Generator                  | 229 |

|     |      | Implementation Complexity                       | 229 |

|     |      | Implementation Restrictions                     | 231 |

|     | 10.8 | Summary                                         | 233 |

| 11  | Ехр  | erimental Results                               | 235 |

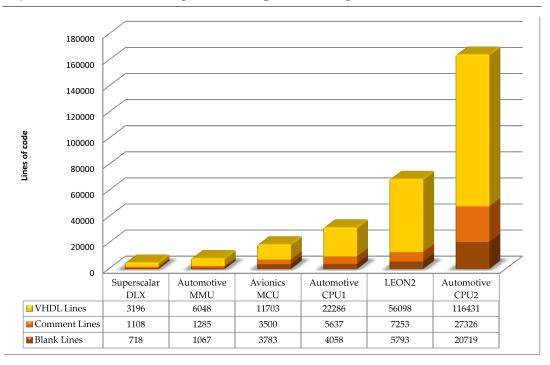

|     | 11.1 | Overview                                        | 236 |

|     | 11.2 | Complexity of VHDL Specifications               | 236 |

|     |      | 11.2.1 Superscalar DLX                          | 237 |

|     |      | 11.2.2 Code Size Comparison                     | 240 |

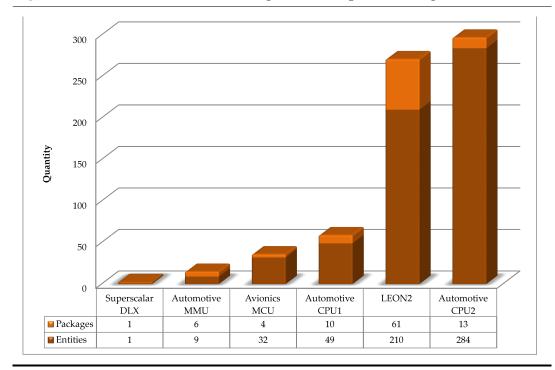

|     |      | 11.2.3 Structural Size Comparison               | 241 |

|     | 11.3 | Derivation Process Complexity                   | 243 |

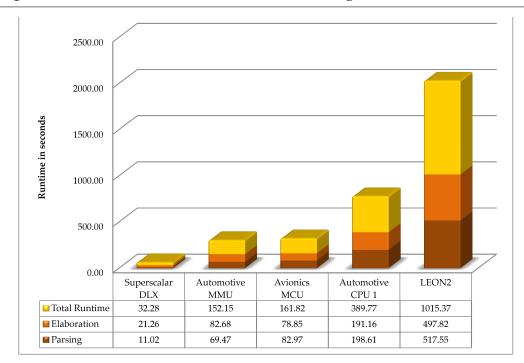

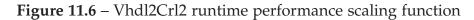

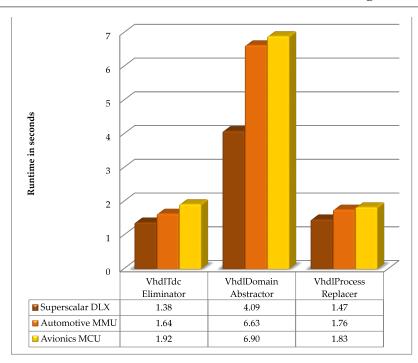

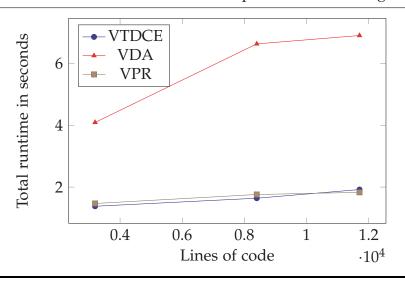

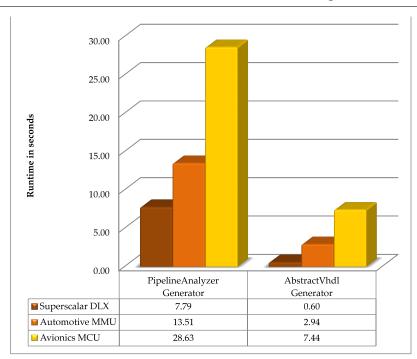

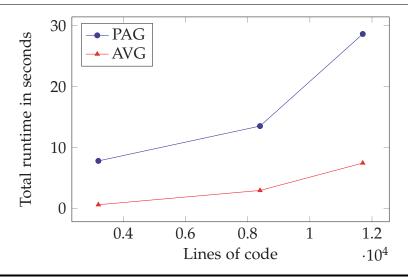

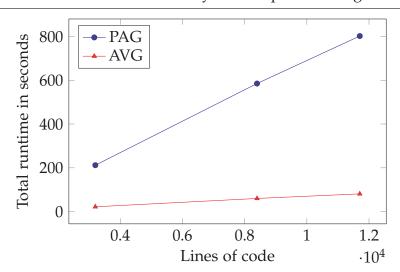

|     |      | 11.3.1 Tool Execution Time Experiments          | 244 |

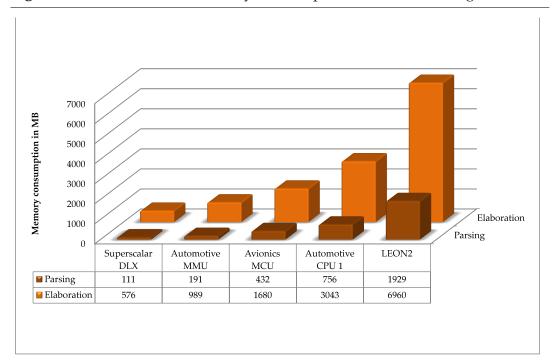

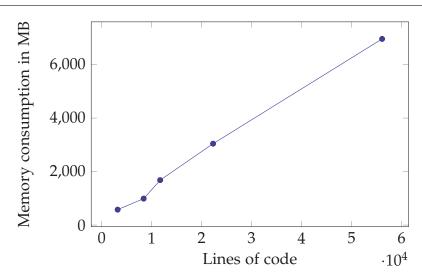

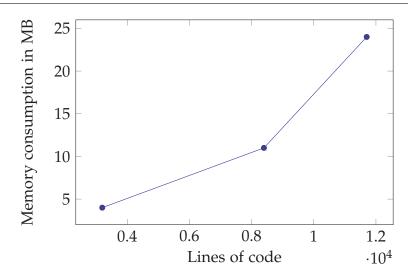

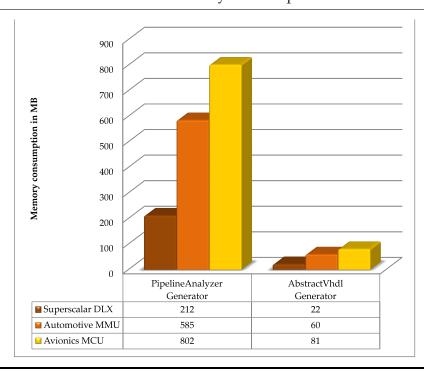

|     |      | 11.3.2 Tool Memory Consumption Experiments      | 251 |

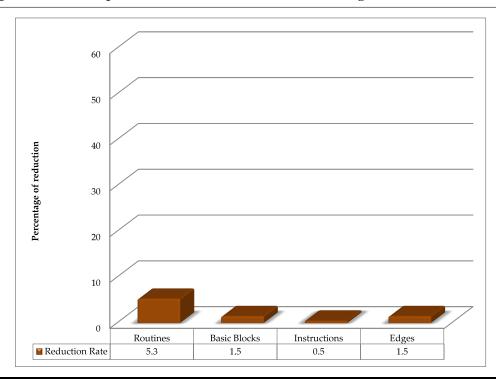

|     | 11.4 | VHDL Specification Size Reduction               | 258 |

|     |      | Precision of Computed WCET Bounds               | 262 |

|     |      | 11.5.1 Superscalar DLX                          | 264 |

|     |      |                                                 |     |

#### Contents

| 11.5.2 Avionics Memory Controller | 266 |

|-----------------------------------|-----|

| 11.6 Applicability and Summary    | 269 |

| 12 Conclusion and Future Work     | 273 |

| 12.1 Contributions of this Thesis | 274 |

| 12.1.1 Timing Model Derivation    | 274 |

| 12.1.2 Simulation Semantics       |     |

| 12.1.3 Timing Model Validation    | 276 |

| 12.1.4 VHDL Predictability        | 277 |

| 12.1.5 VHDL Derivation Tool Set   | 277 |

| 12.1.6 Experimental Results       | 278 |

| 12.1.7 Summary                    | 279 |

| 12.2 Future Work                  | 280 |

| List of Figures                   | 283 |

| List of Tables                    | 285 |

| Listings                          | 287 |

| Bibliography                      | 289 |

| Index                             | 311 |

1

# Introduction

"There is no reason for any individual to have a computer in his home."

(Ken Olson)

## 1.1 Embedded Systems

Since the industrialization, our daily life is more and more influenced by technological innovations. This trend emerges, e.g., the evolution of mobile phones from their original purpose — being able to phone a person more or less independently of the own location — towards small but integrated smartphones allowing their users to not only do phone calls but also to organize their life and thereby integrating business with spare time. But embedded systems support human beings even in less visible areas: namely embedded into larger products like cars, air planes, trains, medical devices and more.

Among those applications, there are the *safety-critical* applications/systems, as e.g., a flight controller in fly-by-wire steered air planes which surely is one of the most prominent and critical examples. Failures of such systems are simply not acceptable and the probability of their occurrence must be at least minimized. Otherwise, their consequences would create high costs or even endanger human life. Therefore, utmost carefulness and state-of-the-art techniques for verifying software safety requirements have to be applied in order to assure an application's proper mode of operation.

## 1.2 Timing Analysis of Embedded Systems

Assuring correctness is not limited to the validation of the program logic of the application. Beyond that, the absence of runtime errors (division by zero, array index over-/underflow, ...) has to be proven [KWN<sup>+</sup>10]. In addition, safety-critical systems are often forced to finish their execution within strict deadlines dictated by the surrounding physical environment. Not to fulfill such deadlines might lead to system errors ending up in hazards that actually compromise the functional correctness of a system. This dependency is also reflected in all current safety standards (like DO-178B [DO92], ISO 26262 [ISO11], IEC 61508 [IEC10], ...) whose goals are to require the system developer to identify both functional and non-functional hazards and to demonstrate that the software does not violate the relevant safety goals. Depending on the criticality level, a sophisticated examination of the timing behavior has to be contributed to show the functional correctness of a safety-critical system, i.e., it has to be proven that the system meets its deadlines even in the worst-case scenario [SPH<sup>+</sup>05]. While the standards do not enforce

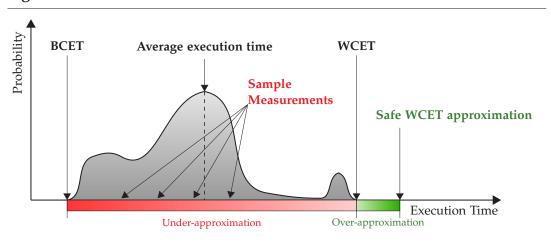

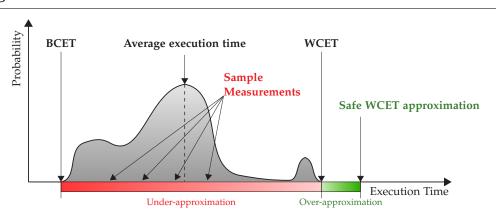

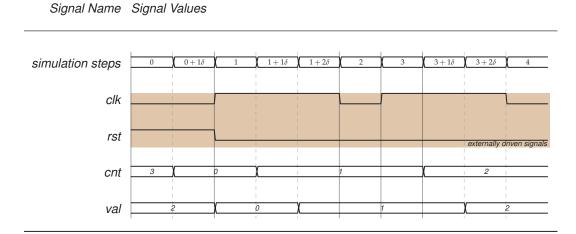

**Figure 1.1** – Execution time distribution

specific testing and verification methods, the importance of static verification is emphasized.

Code level timing analysis addresses the non-preempted execution of a single process, a task or an interrupt service routine. Its results are then used by the system level timing analysis which checks a system of functions or tasks for their schedulability according to a specified scheduling algorithm. This thesis focuses on the code level timing analysis as described in Chapter 4.

## 1.2.1 The Timing Problem

Why is the determination of the runtime of a program a difficult and complex problem?

One might come up with this question. But when starting to think about how to exactly determine a program's execution time, it quickly becomes clear that runtime is not a single and precisely computable value. Figure 1.1 tries to exemplarily illustrate that the runtime of a program or task varies among different executions between a so-called *best-* and *worst-case execution time* which are typically abbreviated with BCET and WCET.

Possible reasons for the execution time's variability are

▶ the input program (size, number of memory accesses, ...),

- ▶ the initial system state (cache contents, hardware configuration, ...),

- ▶ interferences from the environment (preemptions, interrupts, ...).

In general, the concrete WCET cannot be determined for all programs because this would decide the halting problem (cf. Chapter 4). But a suitably restricted subset of programs (no endless loops, no dynamic memory allocation, ...) would at least theoretically allow this computation. However practically, this task is just too demanding from a computational complexity point of view because of the above mentioned uncertainties in the starting state of the system. Additionally, a "brute-force" simulation of all execution paths in the program is not feasible in most cases, as well, since the number of paths grows exponentially with the size of the program [WEE+08]. Any test case selection for a program potentially under-approximates its WCET as long as the corresponding worst-case input (the one triggering the worstcase execution time) is not known. Unfortunately, this worst-case input is unknown for non-trivial software and its determination would require an exhaustive exploration of all program paths. Therefore, it can only be approximated in a safely manner by computing an upper bound on the execution time which is guaranteed to be greater than or equal to all possible execution times independently from the sources of variability. Moreover, the computed bound needs to be precise for industrial applications because large overestimations do not enable users to prove their timing constraints to be met.

A traditional approach for this timing problem has been to partition the application under analysis into code snippets for which the determination of the worst-case input seems to be possible. The execution time of each snippet based on these inputs is then measured and the results are combined to find the global worst-case path together with its runtime. Based on the above described variability of the runtime, this is an error-prone and expensive approach and does not satisfy modern safety requirements. The goal must be the determination of safe and precise upper bounds on the concrete WCET.

## 1.2.2 WCET Analysis by Abstract Interpretation

Most interesting program properties like the WCET are undecidable. Abstract interpretation [CC77, CC92a, CC92b] is a semantics-based methodology for static program analyses where the concrete semantics is mapped to a simpler – abstract – model. Static analysis then determines program properties with

respect to that model. Although mapping concrete to abstract semantics is at the expense of analysis precision, i.e., it leads to over-approximations of the concrete WCET, the computation may be faster. Another advantage is the provable soundness of abstract interpretation-based analyzers. Sound means that its results hold for any program execution and can therefore be used as a safety-guarantee. A WCET bound computed by a sound analyzer will never under-approximate the concrete WCET of the analyzed program. This combination of analysis efficiency and soundness matches the above requirements of timing analyses of safety-critical embedded systems.

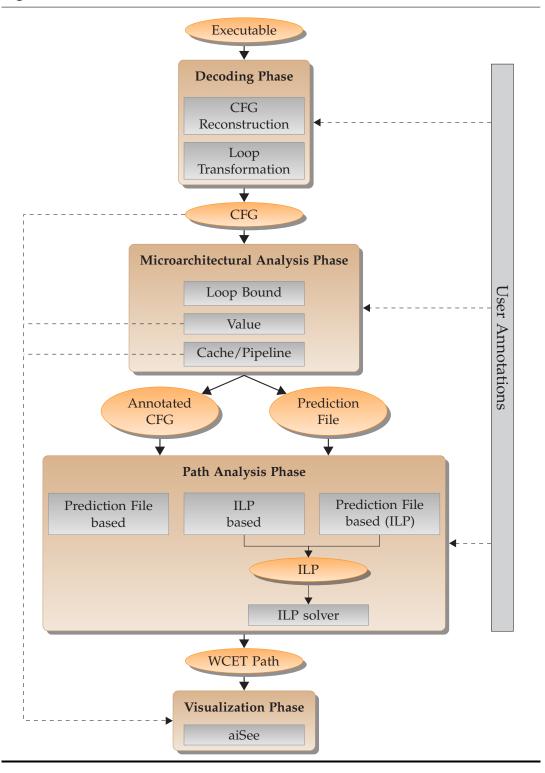

Over the last years, a standard architecture for timing analysis tools has emerged [TFW00, FHL<sup>+</sup>01, Erm03] and consists of the following phases:

- control-flow reconstruction,

- ▶ micro-architectural analysis and

- ▶ path analysis.

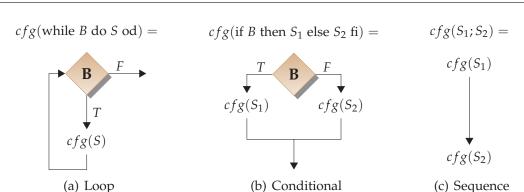

The **control-flow reconstruction phase** operates on the fully linked binary executable and generates a combined call and control-flow graph for its input [The03]. All subsequent analyses are based on this intermediate representation.

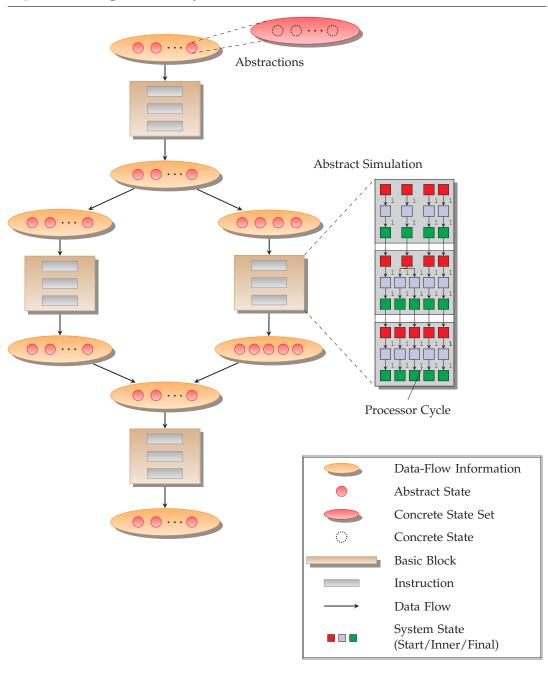

The computationally more intensive **micro-architectural analysis phase** is realized by *abstract interpretations* and has the following three constituents:

- 1. *Loop/Value analysis* attempts to compute information about data accesses and control flow. In particular it tries to identify infeasible paths, i.e., syntactically possible paths that will never be taken because of contradictory conditions. The underlying abstract model is manually derived from the concrete instruction-set semantics.

- 2. Cache-behavior prediction determines a safe and concise approximation of the contents of caches in order to classify memory accesses as definite cache hits or misses.

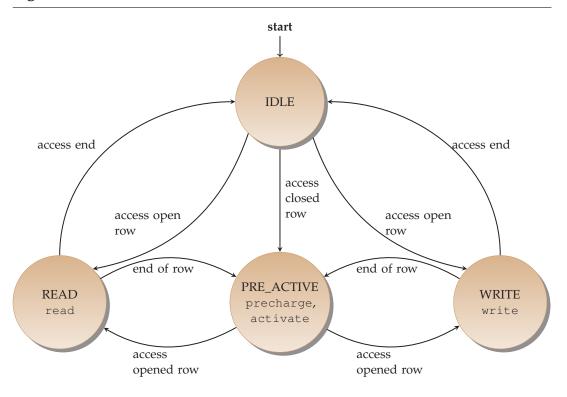

- 3. *Pipeline-behavior prediction* analyzes how instructions pass through the processor pipeline taking cache-hit or miss information into account. There, basic block timings are determined using an abstract processor model (*timing model*) that defines a cycle-level abstract semantics for each instruction's execution yielding in a certain set of final system states. After the analysis of one instruction has been finished, these

states are used as start states in the analysis of the successor instruction(s). Here, the timing model introduces nondeterminism that leads to multiple possible execution paths in the analyzed program. The pipeline analysis needs to examine all of these paths.

The last phase of the timing analysis architecture, the **path analysis**, combines the timing information computed by its predecessor phase to determine the global worst-case execution time for the input program and the triggering path, the so-called worst-case execution path.

The most challenging part of this architecture is the creation of the underlying timing model for the pipeline-behavior prediction because it needs to precisely model the behavior of the processor with its employed memory hierarchy like memory controller, bus system, etc. Depending on the architecture under analysis, the modeled level of detail varies, i.e., for rather simple processors like an ARM7 [ARM00], the analysis "only" needs to count the instructions while applying specific execution latencies. But the unit-time (executing an instruction always takes exactly one time unit) or constant-time abstraction used for simpler architectures is rendered obsolete by the advent of modern processors. With features like branch prediction, out-of-order execution or speculation, the state space of input data and initial states, in general, is too large to exhaustively explore all possible executions and so determine the exact worst-case execution time. Some abstraction of the execution platform is necessary to make a timing analysis of the system feasible. These abstractions inevitably lose information, and yet must guarantee upper bounds for the worst-case execution time.

The aiT WCET analyzer developed by AbsInt GmbH and Saarland University is a prominent timing analysis tool that implements the above described architecture. It has been used in international industrial and research projects, e.g., Verisoft, Verisoft XT [Ver], PREDATOR [PRE], INTERESTED [INT], ..., and has been used in the certification of safety-critical industrial systems, e.g. [SPH+05]. Therefore, the implementations that are contributed by this thesis, are realized on top of the AbsInt tool chain for WCET analysis, which is detailed in Section 4.3.

## 1.3 Deriving Timing Models

Currently, the timing models described above are *hand-crafted* [SP10] by human experts based on

- ▶ processor/system documentation and

- ► reverse engineering by runtime measurements.

Although the hardware manufacturers are usually cooperative and provide internal and partly confidential documentation, there is the drawback that those documents usually contain errors or leave out some important details. Traces of specific runtime measurements on partly hand-written assembler code should fill this gap. Depending on the hardware architecture, those traces might only show end-to-end timings or timestamps of active bus transaction signals (cf. Section 8.2.2). Sometimes, it is also possible to monitor processor core internals by so-called performance monitoring features within the hardware (cf. Section 8.2.1).

This basis for the development of timing models renders the model engineering as well as the implementation of the corresponding pipeline analyzer to be a time-consuming, complex and error-prone process. Creating such a timing model from scratch for a modern and complex processor like the Freescale PowerPC 7448 [Fre05a] might consume 3–4 man-months even for rather experienced people.

Nowadays, hardware circuits are automatically synthesized from formal hardware specifications like VHDL or Verilog (cf. Section 5.3). Besides a formalization of the functional details, such specifications implicitly contain an execution model that also reflects the timing behavior of the whole system. This enables the derivation of timing models based on their formal hardware specification to simplify the above described error-prone development process. Moreover, this bridges the gap between hardware circuit synthesis and WCET analysis development and constitutes one of the major contributions of this thesis.

### 1.4 Contributions

In the context of timing analysis for safety-critical embedded control software and the development of the required timing models, the contributions of this thesis are outlined below. Additionally, a differentiation between the present thesis and the work of Schlickling [Sch13] is given where appropriate.

### 1.4.1 Timing Model Derivation

Static analysis and model transformations are employed to extract the timing information of hardware circuits from its formal specification. Where Schlickling [Sch13] introduces abstract interpretation-based static analysis of formal hardware models, this thesis focuses on the derivation process as a whole. Starting from the hardware model, transformations and abstractions based on the results of static analyzers extract the timing-relevant information, the timing model. In the end, an aiT-compatible pipeline analyzer can be generated from such a model.

**Semantic Level Reduction** A prerequisite for the application of both static program analysis and transformations is a common intermediate representation of the hardware model. Because the chosen analysis approach, abstract interpretation, has its origins in program analysis, the hardware model needs to be represented as a sequential program. Although hardware descriptions are concurrent models, i.e., their processes are designed to run in parallel, such a conversion is possible because their two-level semantics allows to choose an arbitrary execution order of the processes (cf. Section 5.2.3). Thus, this thesis defines translation rules to convert VHDL language constructs into control-flow entities combined with a framework of generated routines, so that the resulting control-flow representation forms a simulation environment for the original hardware design. On top of that, abstract interpretation-based static analyzers [Sch13] are enabled to examine the model and result communication is possible via a shared intermediate format called CRL. This translation from VHDL into a sequential execution model is called semantic level reduction (cf. Section 6.3.2) and is generic enough to be applied to related hardware description languages like Verilog, as well.

**Derivation Process Definition** As these hardware specification languages have been partly designed for integrated simulation of the specified circuits [Ash08], the question might come up here whether it would not be possible to just use these simulation capabilities to determine execution costs of critical tasks. The answer is that VHDL models of real-world processors are usually big and complex making WCET determination a difficult task [SP10]. In the presence of the uncertainties described above like nondeterministic system starting states, a static timing analysis based on the unchanged formal hardware specification would be infeasible in terms of space and analysis

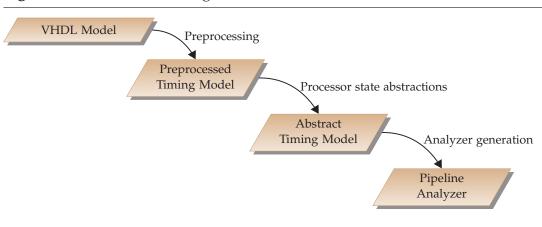

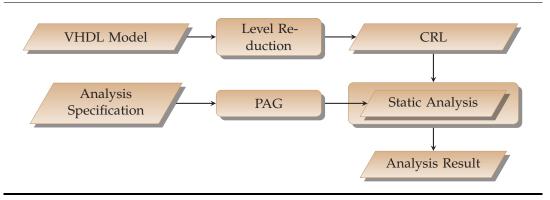

Figure 1.2 – Sketched Timing Model Derivation Process

time consumption. Furthermore, the VHDL code cannot be used "as is" for a static timing analysis because such a simulation cannot cope with "unknown" data, e.g., unknown cache contents.

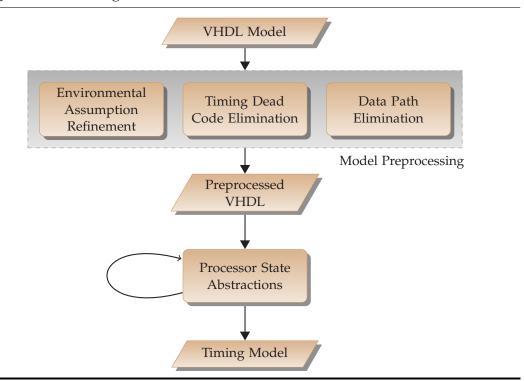

Therefore, a distinct process for extracting timing-relevant information is necessary which is one of the main contributions of this thesis. Figure 1.2 shows a structural picture of this process.

In a first step, the size of the model is reduced by pruning out all parts that do not contribute to the timing behavior at all. For example, there is no need for information about each step within a multiplier unit. Instead, it suffices to know the number of clock cycles each stage of the multiplier pipeline is occupied by a specific instruction. The pruned model still contains a lot of detailed information about the processor state. But for practical reasons it is impossible to represent all state information in full detail. For example, if the contents of all memory cells or registers should be modeled in all details, the resulting space requirements would be prohibitive for non-trivial architectures. Fortunately, the exact knowledge about such details often is not important as far as timing is concerned: an addition always takes the same amount of time, no matter what the arguments are. In other cases, the timing does depend on such information, but a loss of precision is acceptable in order to make the analysis more efficient, or even possible at all. One example for this situation are multiplications on some architectures which are faster if one argument has leading zero bits. By not keeping track of the arguments exactly, an entire range of execution times has to be assumed for multiplication. The loss in precision is acceptable in this case as the difference

usually is below ten processor cycles and multiplications are in general rare. Therefore, abstractions from the concrete model are introduced, i.e., some details of the processor state are left out or will be approximated. Using the methodology of abstract interpretation, one can trade precision of the analysis against efficiency by choosing different abstractions and concretion relations between the original and abstract model. Finally, an aiT-compatible pipeline-behavior analysis is generated from the timing model in the last step that concludes the derivation process.

**Derivation of Workflow Patterns** The derivation process described above represents a general methodology. But the particular abstractions and transformations depend on the concrete hardware architecture whose timing behavior has to be modeled so that the invention of these abstractions remains an intellectual challenge. However, typical working patterns came up during the implementation/experiments and are described in Section 6.5.

The model preprocessing phase is realized by assigning fixed values to signals/variables so that a subsequent constant propagation effectively renders parts of the specification unused – *timing dead*. Their transitive closure can then be removed automatically. Inventing assumptions about the model is an iterative procedure and coupled with feedback from an interactive exploration and understanding of the hardware design that can be reached using the level-based slicing tool developed by Schlickling [Sch13].

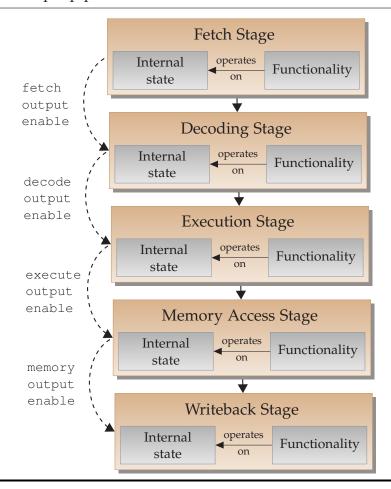

In principle, a processor's timing behavior is dominated by the (timing-)effect of the instruction flow through the processor pipeline and latencies for memory accesses. Therefore, the resulting timing model needs to represent this flow. Required combinations of program slices and additional model assumptions can be used to extract this information. They are described in Section 6.5.1.

After model preprocessing, abstractions may be applied to further reduce the resulting timing analysis' complexity. Three different kinds of abstractions are proposed:

- ► *Memory abstraction*

- ▶ Domain abstraction and

- ► Process replacement

The memory abstraction aims at removing all data paths from the hardware model. Instead, queries to the value analysis results (cf. Section 1.2.2) are inserted appropriately. Domain abstractions perform source-to-source type transformations. A prominent example is the so-called address abstraction where concrete addresses are replaced by abstract values standing for certain sets of concrete values. Process replacements enable the integration of custom simulation routines into the timing model. They substitute VHDL processes by simplified code snippets. Typically, these snippets specify the timing effect of the replaced process and remove purely functional code. For example, the functionality of a simple arithmetic unit can be replaced by a small component with a timer. It is started for an instruction newly entering the unit and simulates their execution time because this is the essential information within the timing analysis.

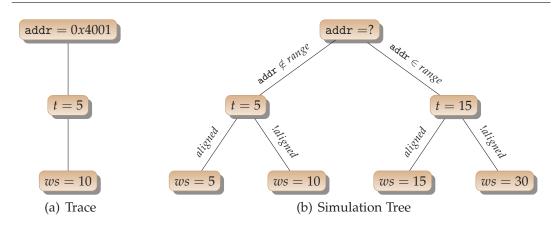

#### 1.4.2 Simulation Semantics

A pipeline-behavior analysis is an abstract (and thereby computable) simulation of a program's execution. The generated analyzer is based on a corresponding abstract simulation semantics that is constructed throughout Chapter 7: An operational semantics for the simulation of non-abstracted VHDL models is formalized and followed by an abstract variant so that the pipeline analyzer's abstract simulation safely approximates any concrete simulation. Employed abstractions can render the model nondeterministic, i.e., the simulation process might compute multiple successors for a given input system state leading to multiple possible execution paths partially with different costs in terms of execution time. The defined abstract simulation semantics is able to cope with such uncertainties and simulates all potential execution paths.

## 1.4.3 Timing Model Validation

The derived timing model per construction is a correct representation of the underlying hardware's timing behavior and the defined abstract simulation semantics is a sound approximation to any concrete simulation. Concerning the correctness of the resulting pipeline-behavior analysis, it remains to show that the employed model abstractions and transformations do not introduce unsafe<sup>1</sup> changes to the timing behavior. Interval property checking techniques

<sup>&</sup>lt;sup>1</sup>under-estimations

(IPC) [Bor09] from the area of formal functional hardware verification fit that purpose because they are able to show the "timing-semantic" preserving translation from the input design to the timing model. Thus, this thesis contributes approaches for the validation of derived timing models based on IPC.

Additionally, complementing validation techniques are presented where confidence on the correctness is achieved by testing. Measurement capabilities can produce runtime observations at different levels that are compared to the corresponding prediction of the timing analyzer. Sample levels are processor core events like cache hits and number of dispatched instructions at a specific execution point or visible bus transaction signals triggered by memory accesses.

### 1.4.4 VHDL Predictability

Experiments with different VHDL models have revealed that the quality of the derived timing model (in terms of the precision of computed WCET bounds as well as the computational complexity) is influenced by the VHDL coding style. This thesis describes design choices together with their effect on the derivation process and thereby formulates a kind of predictability notion for VHDL language constructs along with advices to the corresponding hardware development. Minimal dependencies between processes, a clear logical separation of different functionality into different processes/subprograms and a sequential logic design are the most prominent and important properties which support and simplify the semi-automatic derivation process.

#### 1.4.5 VHDL Derivation Tool Set

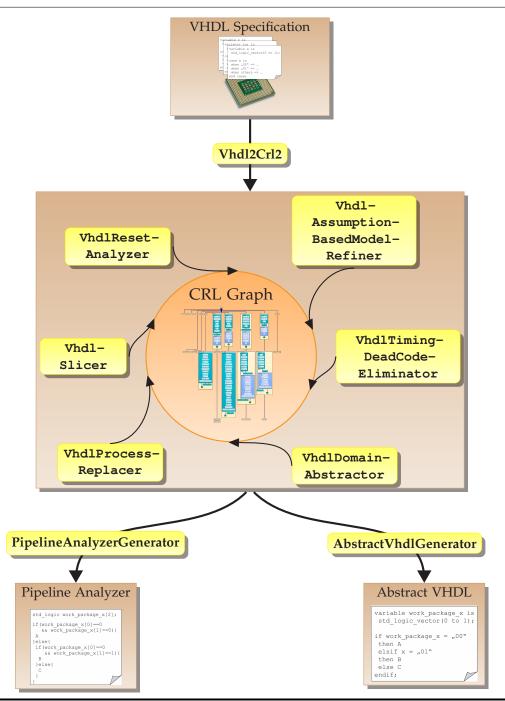

The timing model derivation process has been realized by the implementation of a set of tools:

- ▶ a VHDL compiler,

- ▶ abstract interpretation-based static analyzers,

- model transformation tools,

- ▶ a pipeline analyzer generator and

- ▶ an abstract VHDL generator.

The VHDL compiler is called Vhdl2Crl2 and transforms an input VHDL design into its equivalent representation as a sequential program. By this, it implements the semantic level reduction that has been mentioned at the beginning of this section. All analysis and transformation tools operate on the generated CRL representation (cf. Section section 1.4.1 on page 8) that serves as an exchange format.

Three static analyzers are employed during the derivation process: Vhdl-ResetAnalyzer, VhdlAssumptionBasedModelRefiner and the VhdlSlicer. The first two tools deal with the computation of initial signal assignments and the identification of unused code snippets based on given signal assumptions, respectively. Model exploration and understanding is supported by the slicing tool. All three have been developed by Schlickling [Sch13] and are used within the defined timing model derivation process.

Three model transformation tools are contained in the tool set: Vhdl-TimingDeadCodeEliminator incorporates the results of the assumptionbased model refiner by automatically removing the transitive closure ("timingdead propagation") of all marked CRL entities. By this, it effectively reduces the size of the model. **VhdlDomainAbstractor** implements automatic type changes to signals or variables of a design as a source-to-source translation where the destination domain has to be specified by the user. For example, an integer data type might be transformed into a custom-defined abstract data type representing an interval of integers. Expressions using variables/signals whose type has been transformed to the specified target domain are potentially invalid as the standard operators might not be defined for the specified target domain. In such cases, alternative operators have to be provided by the user. To support this need, the tool prints signatures of needed operators as a result of the transformation. Additionally, different application scopes are supported, i.e., the transformation effect can be restricted to a specified set of identifiers. By this, the model can be iteratively transformed. Vhdl-**ProcessReplacer** automates the replacement of VHDL processes by custom simulation routines which are provided by the user.

The pipeline analyzer generation tool is called **PipelineAnalyzerGenerator** and realizes the abstract simulation semantics contributed by this thesis and mentioned above. A reconstruction of the timing model into an abstract VHDL can be performed by the tool **AbstractVhdlGenerator**. Its purpose is to establish a link between the derived timing model in its CRL representation and the validation of the employed model transformations because the above

mentioned interval property checking techniques are implemented within a VHDL-reading analyzer.

### 1.4.6 Experimental Results

Experiments with the tool implementations have been conducted to underline the industrial applicability of the approach in total.

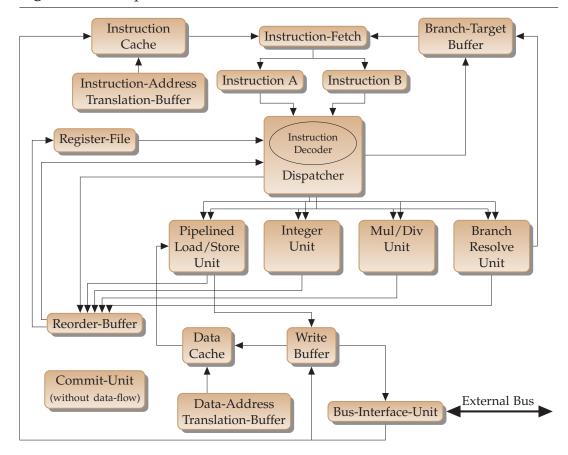

The following VHDL designs have been examined:

- ▶ a superscalar DLX variant similar to a PowerPC 603e,

- ▶ the SPARC V8 architecture based LEON2 processor (typically used in aeronautics applications),

- ▶ a memory controller used within modern avionics systems and

- ▶ two representative automotive processors.

Except the first one, all these models represent processors or memory controller specifications that are utilized within real-world safety-critical systems. The superscalar DLX machine is an implementation from the Technical University of Darmstadt [Hor97] that is based on the DLX presented by Hennessy [HPG06]. Although the design is not industrially used, it offers features like out-of-order execution, speculation and branch prediction. Non-disclosure agreements with the particular manufacturers forbid the exposure of the original names for the anonymous avionics and automotive designs.

Runtime and memory consumption experiments show a good performance of the implemented tools along with a linear scaling in the code size on the selected hardware models. Even big processor specifications like a LEON2 (with about 70 000 lines of code) can be translated into their sequential program representation within acceptable time (about 17 min for the LEON2). The memory consumption is high with about 7 GB but this has been expected regarding the transformation's complexity. Resource consumption of the transformation and generator tools is low compared to the VHDL compiler and dominated by the size of the intermediate representation. Execution times are just below 30 s and the maximal observed memory consumption is 802 MB in the experiments.

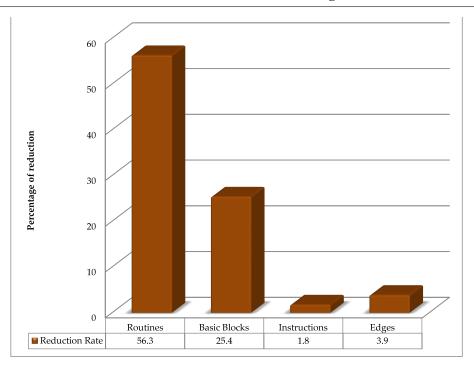

During the derivation process employed model transformations are shown to reduce the size of input VHDL models (around 50 % for a modern memory

controller of an avionics system) enabling the generation of aiT-compatible pipeline analyzers.

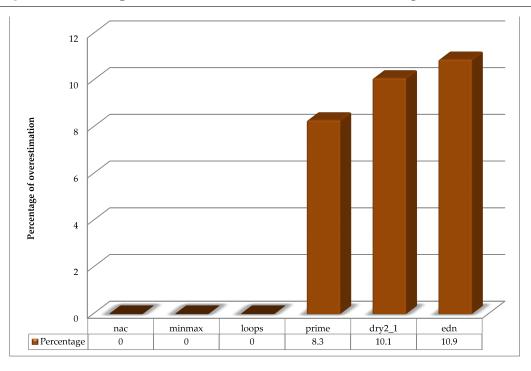

Moreover, there are two different kinds of experiments underlining the competitiveness of derived timing models against hand-crafted ones. For the superscalar DLX, synthetic execution traces retrieved by VHDL simulations have been compared to the predictions of the corresponding generated timing analyzer. Results show an average overestimation of around 10% for the predictions. Additionally, the semi-automatically derived timing model of the avionics memory controller is qualitatively compared to an existing hand-crafted model where the term hand-crafted in this case means that the model has been developed by a manual examination of the controller's VHDL design. Computed WCET bounds either are equal or over-estimate the legacy bounds only by a small percentage (less then 1%).

### 1.5 Thesis Outline

After this introductory chapter, a classification of related work is given in **Chapter 2**.

Chapter 3 develops a terminological basis for "embedded systems" with its characteristic properties including typical application areas. Moreover, it introduces current hardware architectures and processor pipelines for such systems with their performance enhancing features.

The current state-of-the-art in timing analysis of embedded systems is described in **Chapter 4**. First, there is an overview of the different existing approaches and after that, the structure and functionality of the aiT framework is presented in detail.

In **Chapter 5**, formal hardware specification languages are introduced with the example of VHDL. Typical language constructs and the two-level semantics are explained and the automated synthesis of hardware circuits from formal specifications is address, as well.

**Chapter 6** contains a detailed description of the workflow for timing model derivation.

**Chapter 7** shows how to generate a pipeline analyzer from a derived timing model.

In **Chapter 8**, methods for the validating timing models are presented.

Considerations about timing predictability of hardware components and the impact of certain language constructs on the predictability of a derived timing model is detailed in **Chapter 9**.

After that, **Chapter 10** presents the VHDL derivation tool set implementation with the structure of the contained tools.

Corresponding experimental results on industry hardware models are then shown in **Chapter 11**.

Finally, **Chapter 12** concludes this thesis and gives an outlook to potential future work.

2

# **Related Work**

"Honos reddatur dignis."

This chapter describes work related to this thesis and points out the particular relation. In parts, this relations are already picked up in other chapters by citations.

The first part addresses the worst-case execution time determination and gives an overview of existing tools and techniques in this area. Because the implementations presented in this thesis base on the aiT WCET analyzer framework, a specific chapter has been dedicated to it. Thus, aiT is not mentioned in this chapter.

In Section 2.2, there is a short introduction to research work about the analysis of formal hardware specifications, in general, but also with the intention of proving safety properties.

The last section in this chapter lists capabilities of hardware simulators and discusses the difference between such a concrete system simulation and the abstract simulation performed by the combined cache and pipeline analysis as presented in Section 4.3.3.

## 2.1 Worst-Case Execution Time Computation

As detailed by Wilhelm [WEE<sup>+</sup>08], there are numerous tools around that are concerned with the determination of upper bounds on the execution time of tasks within embedded systems. In the following, a short description of the most prominent and usable tools is given. More details and references can be found in the WCET tool survey [WEE<sup>+</sup>08] and WCET Tool Challenge report 2011 [HHL<sup>+</sup>11]. According to the theoretical considerations on timing analysis in Section 4.2, existing methods can be categorized into two major groups, static and dynamic methods. Whereas approaches in the first group are based on static analysis of binary executables and/or source code, the second represents dynamic methods relying on runtime measurements to determine the timing bounds. In the end, there is another group, called the hybrid methods which try to combine both worlds in order to overcome their specific limitations.

#### 2.1.1 Static Methods

Besides the aiT WCET analyzer which is described in detail in Section 4.3, there are other WCET tools that are based on static analysis. The following

sections describe all available tools that have participated in the WCET tool challenge 2011 [HHL<sup>+</sup>11] with the exception of aiT which is described in Section 4.3 in detail.

#### **Bound-T**

*Bound-T* [HS02] has originally been developed at Space Systems Finland Ltd. for the verification of software running in spacecrafts. Currently, Tidorum Ltd. has taken over the development.

Bound-T is based on the binary executable from which the control-flow graph is reconstructed by a decoding process. After that, static analysis like constant and copy propagation is performed and integer computations are modeled as transfer relations described by Presburger arithmetic formulas [KK67]. These transfer relations are then analyzed in order to identify loop induction variables and bounds as well as the resolution of dynamic branches. The worst-case execution path and its costs are then determined by implicit path enumeration [LM95] which is applied to each subprogram separately.

Neither caches nor dynamic hardware components like caches or out-of-order execution pipelines are considered by Bound-T.

#### **METAMOC**

METAMOC [DOT+10] is a research prototype from Uppsala university in Sweden that has been developed on top of the UPPAAL model checker. Its tool chain consists of the following different analyses: control-flow analysis, value analysis and pipeline analysis. During control-flow analysis, the input binary executable is translated into its assembly representation. The value analysis analyzed the assembly representation and determines an approximation to register values and addresses of accessed memory cells for each program point. Flow information like loop bounds that cannot be automatically computed, have to be specified by the user. The control-flow graph of the decoded assembly is reconstructed and represented as an UPPAAL model. This model is combined with a model of the underlying hardware architecture (given by the user as networks of timed automata [DOT+10]) so that the resulting model can be checked using the UPPAAL model checker whose final result is the WCET bound.

Exposing the hardware model to the user demands for a detailed knowledge about the hardware's behavior. The authors of METAMOC state that modeling complex and timing anomaly exhibiting [RWT<sup>+</sup>06] processors push the underlying model checker to its limits [DOT<sup>+</sup>10]. Similar consequences might result from imprecise flow information.

#### **OTAWA**

OTAWA [BCRS10] is an open-source framework library from IRIT and University of Toulouse intended to support the development of WCET analyzers operating on the binary executable. The supported tool chain is similar to the one of the aiT framework, i.e., a decoding phase to reconstruct the control flow of the input executable is followed by micro-architectural analyses for the determination of flow facts and execution timings based on the previous analysis results.

A generic kernel with defined interfaces allows the integration of different analyses implementations which makes the framework extensible. Functionality for loading binaries of certain architectures like PowerPC, ARM, TriCore, Sparc and HCS12 is already available. Additionally, loaders of user annotations for flow facts (loop bounds, branch targets or custom flow constraints, ...) and custom information on each control-flow graph node exist. The actual development of a timing analysis is supported by an interface that allows to plug in different WCET computation models. From that point of view, OTAWA is not a stand-alone WCET analyzer by itself.

Proof-of-concept analyzers have been implemented and participated in the WCET tool challenge 2011 [HHL<sup>+</sup>11]. There, they are described to have problems with unsupported instructions and not automatically computed flow facts.

#### **SWEET**

SWEET [Erm03, ESG<sup>+</sup>07] is the abbreviation for *Swedish Execution Time Tool* which has been developed and maintained by the Mälardalen WCET research group. SWEET operates on a custom intermediate program representation format called ALF. Its tool chain is similar to the one of aiT and consists of three phases:

- ▶ A *flow analysis* phase which consists of program slicing, pattern matching and abstract execution (symbolic execution based on abstract interpretation). It is used to determine flow facts on the analyzed program like loop bounds. These flow facts are usable only if the input program has been compiled with the integrated SWEET research compiler. Otherwise, all flow information must be given manually.

- ▶ Processor-behavior analysis that consists of a memory-access analysis to identify the memory accessed by instructions and a pipeline analysis performing a simulation of the analyzed program based on a cycle-accurate model of the architecture with the determined flow analysis results as additional input. This analysis phase only supports instruction caches and in-order processors with bounded long-timing effects and no timing anomalies (cf. Section 6.2.2). Out-of-order execution is explicitly not supported.

- ► Estimate calculation phase that actually calculates the worst-case execution path with its costs using implicit path enumeration [LM95] as well as fast local-path techniques.

#### **TuBound**

TuBound is a research prototype from Vienna University of Technology [PSK08]. The idea behind that tool is that annotations and optimizations can be made at the source code level while the actual timing analysis still happens at the object code level. Source code is parsed with the C/C++ frontend from the Edison Design Group into a syntax tree format which is analyzed with an inter-procedural interval analysis generated by the program analyzer generator PAG [Mar99]. By this, value ranges of variables are attached to the syntax tree. Then, loop bounds are determined via equation system solving and constraint logic programming on this annotated syntax tree which results in annotated flow constraints. After that, the input program is optimized by the ROSE source-to-source transformation and optimization framework while the annotated flow information is changed accordingly. The optimized program code is then processed with a modified compiler that preserves the annotated flow information. Worst-case execution times of basic blocks are computed by instruction table lookups which effectively prevents to model complex processor architectures with superscalar pipelines and related performance-enhancing features. The global worst-case execution path is then computed via integer linear programming over the combined equation

system of basic block execution times, control-flow graph connections and annotated flow constraints.

#### **WCA**

WCA is research prototype of a static WCET analysis tool for the JOP architecture [SPPH10]. Tool inputs are a processor specification and the java bytecode that is executed on the architecture. Additionally, annotations from the java source code can be loaded. For the execution timing, data-flow analysis is employed first to obtain loop bounds and branch targets (for dynamic method dispatching). After that, a pipeline analysis derives symbolic formulas of the worst-case execution time of bytecode instructions. WCA only supports a subset of C, called wcetC, enhanced by extensions for flow annotations. According to [HHL+11], the tool cooperates with a modified version of the GNU C compiler that performs abstract co-interpretation during code translation yielding an integer linear program. That program in the end is solved by an ILP solver to compute the overall timing bound.

### 2.1.2 Dynamic Methods

The counterpart for the above described static methods is the dynamic method. In this section, some existing tools implementing such approaches are shortly presented. Their common property is that they do not rely on static analysis to obtain the worst-case timing bounds. Instead, they basically perform runtime measurements of the analyzed program and try to infer WCET estimations from them.

#### Research Prototype from TU Vienna

The research prototype from TU Vienna [PN98] has no explicit tool name. Its approach is to iteratively perform runtime measurements for the computation of a WCET estimate where genetic algorithms are used to provide the input data for that measurements. An evaluation of the computed timing estimates steers the repeated generation of new input data for the next iteration of measurements. To stop the iteration, a termination criterion has to be specified by the user. As described in Section 4.2.2, such an approach cannot assure any safety guarantee on the worst-case execution time of a program, in general.

# 2.1.3 Hybrid Methods

The third category of WCET computations are the hybrid methods. They combine static analysis with runtime measurements.

# RapiTime

RapiTime [BCP02] is the commercial version of a research tool from the University of York and distributed by Rapita System Ltd. It computes the distribution of the execution time for basic blocks of a program by performing runtime measurements where the corresponding program input has to be provided by the user. The needed runtime traces can be obtained by techniques like code instrumentation (optionally with external hardware support), non-intrusive tracing techniques (e.g. Nexus traces) or cycle-accurate simulator traces. Basic block execution times are then combined using an algebra of probability distributions [WEE+08].

### **FORTAS**

As described by Hanxleden [HHL<sup>+</sup>11], *FORTAS* [CG11] uses a combination of measurements and static analysis where the traditional measurement-based approach is augmented by a feedback loop implemented by iterative refinements of the measurement inputs. The tool still has a prototype status.

# Research Prototype from TU Vienna

TU Vienna has developed another research prototype [WRKP05] in addition to the one already mentioned above under the dynamic methods. This one uses static analysis of the source code to partition the analyzed program into segments of reasonable size and therefore yields a set of execution paths and information on infeasible paths. For each path, a model checker generates test data serving as inputs for measurements on the corresponding paths. The global WCET estimate is then computed using integer linear programming. As the flow information is based on a source code analysis, it has to be assured that the compiler does not change the program's structure. Path coverage is ensured by the static analysis part, but in the presence of complex processor pipelines, the execution time strongly varies depending on the

input state. Due to this, the needed state coverage is not provided by the tool.

# 2.2 Analysis of Formal Hardware Specifications

As the timing model derivation approach presented in this thesis uses formal hardware specifications as the starting point, it is interesting to distinguish it from other research work or tools that are concerned with the analysis of specification models in VHDL, Verilog or similar formal hardware specification languages.

# 2.2.1 Functional Verification

### **Formal Functional Hardware Verification**

Another kind of analysis on hardware specifications exists in the area of formal functional verification where the correctness of a model according to a given specification, like the instruction set semantics, is proven. The employed methods are variants of (bounded) model checking which is common in this area. Details about the state-of-the-art in functional verification of hardware designs, *Equivalence Checking*, are presented in Section 8.3, so further descriptions are omitted here.

### **Testing-based Validation**

Besides formal verification techniques, "simple" testing is still widely used for showing correctness properties of a circuit design. Here, the key point for the testing scenarios is the coverage of the test cases on the specification code. Therefore, tools examine such metrics for a given set of tests, for example

- ▶ the tools distributed by TRANSEDA (http://www.transeda.com) or

- ▶ the open-source tool *covered* (cf. http://covered.sourceforge.net).

More tools are available especially in the embedded system community. Often, this functionality is integrated into commercially available development suites for hardware circuits including synthesis tools.

### **Timed Automata**

In [Neh04], VHDL models are transformed into timed automata specifications by a tool called *VAT*. The overall goal is to apply existing analysis techniques for such automata to hardware specifications in VHDL. Exemplarily, the finite state machine generated by VAT can be checked with the UPPAAL model checker [BLL<sup>+</sup>96]. In principle, the provided functionality seems to be directly related to the VHDL frontend Vhdl2Crl2 from the VHDL derivation tool set introduced in Chapter 10 if one abstracts from the concrete output syntax of the automata and the CRL files. The difference lies in the type of intermediate representation of the analyzed model. Where Vhdl2Crl2 generates a control-flow graph like description of the VHDL design, VAT generates timed automata that can be processed directly by a model checker.

# **Information Flow Analysis**

T. Tolstrup presents an approach [TN06] to detect security leaks in VHDL specifications due to differences in the execution time. The idea is that the timing of cryptographic algorithms often varies depending on the input, e.g., a password or a key. An "observer" then might retrieve such passwords or keys by precisely examining the execution time differences for different inputs. A data-flow analysis is presented that could detect such possibilities by analyzing the timing difference between all paths along which an input signal can flow through the system until it reaches the modification of an output signal. Despite of its nature as a data-flow analysis, this kind of analysis is similar to a WCET analysis as the execution of a program induces signal changes in the hardware model which are integrated in the abstract simulation. It therefore might be possible to implement the proposed analysis in the environment of the VHDL derivation tool set.

# **Abstract Interpretation of VHDL**

Charles Hymans has introduced an abstract interpretation of VHDL models that computes an approximation on the states reachable during the simulation of such a design [Hym02]. A trade-off between precision and computational complexity can be reached by changes to the employed abstract domains. In principle, its method is similar to the pipeline analysis used in the aiT framework (cf. Section 4.3.3). The difference to the timing models used there

is that Charles Hymans' work does not transform the input hardware model in any way. As in this thesis, the only purpose of the timing models is to be used for the computation of WCET bounds, the original model can (and from a complexity point of view must) be freed of all artifacts that do not contribute to the timing behavior of the specified hardware.

Hymans gives a definition of simulation semantics for VHDL language constructs including all types of expressions. In this context, he defines some predicates that have been used by the simulation semantics in Chapter 7:

### $\triangleright$ next:

This predicate returns the next statement based on the current simulation position.

### **▶** *eval*:

Evaluation of VHDL expressions is embedded into this predicate.

### **▶** wake:

Repeated process execution after a value change in at least one of the signals in the process' sensitivity list is embedded in this predicate. The analogous operator in this thesis is called *repeat*.

# 2.3 Hardware Simulation

In addition to the different WCET tools described above in Section 2.1, there are simulators for VHDL (or similar hardware description languages) available which can be used for debugging and exploration purposes of a hardware design. In principle, the functionality of these tools is partly equal to synthesis tools as the design has to be loaded and elaborated before it can be simulated. Available tools come from two different communities, namely the academic world and some commercially distributed simulators. One representative for each community is shortly described in the following.

# 2.3.1 GHDL

is an open-source implementation of a VHDL frontend which has a high acceptance, i.e., nearly the whole synthesizable VHDL subset is supported. The design is directly compiled into an executable using the GNU compiler

collection (GCC)<sup>1</sup> whose execution represents the simulation of the hardware circuit. There is no integrated visualization feature like a graphical user interface for an exploration of the model, but timing diagrams for signal values over simulation time can be generated.

Due to the integration with GCC, there is neither any direct access nor an interface to the parsed VHDL design, although this is actually not needed for a simulation, it effectively prevents the tool's use for the timing model derivation purposes introduced by this thesis. For that, dedicated control over the generated intermediate representation is required because the different analyses and transformations need to store custom data.

# 2.3.2 ModelSim

The tool *ModelSim* is distributed by Mentor Graphics [Men08] and is one representative solution for an industrially available simulation tool. It supports even the newest version (from 2008) of the VHDL standard as well as (System-)Verilog and can be used for interactive debugging and exploration by featuring a sophisticated graphical user interface. Furthermore, ModelSim has an integrated heuristic to determine a topological order of the different VHDL modules. This is a convenient feature because most of the existing tools let the user determine the order in which the different VHDL files are fed to the parser. And depending on the hardware to be modeled, such dependencies can become rather complex and unclear. Due to its features, ModelSim can be used for a testing-based functional verification in addition to "simple" model simulation. But as with , there doesn't exist any externally accessible interface to internal data structures of a loaded hardware model.

# 2.3.3 Summary

Besides the two given examples for hardware simulators, there are others available. For a potential usage for the derivation of timing models from formal hardware specifications, there was always the problem of not having access to the internal data structures of a loaded design. This actually is the reason why Vhdl2Crl2 (cf. Chapter 10) has been developed. Due to cost reasons, an evaluation of different synthesis tools has not been performed.

<sup>1</sup>http://gcc.gnu.org

Another common problem especially for the freely available tools is that they most often do not accept the full synthesizable VHDL subset.

In general, hardware simulation is no alternative for analyzing the timing behavior of systems because:

- ▶ Modern real world processors (like Freescale PowerPC 755 [Fre01]) are far too complex. The computational complexity of the simulation would render the method infeasible for industrial usage.

- ▶ Due to the complexity of the problem, nondeterminism is introduced into the computation model. No traditional VHDL simulator can cope with that.

To the best of the authors knowledge, nobody has tried before to automate (at least partly) the development process of a timing model for processors with the goal of WCET determination.

3

# **Embedded Systems**

"I wanted to change the world. But I have found that the only thing one can be sure of changing is oneself."

(Aldous Huxley)

This chapter gives an introduction to *embedded systems* in general, starting from a definition, listing common characteristics of such systems in Section 3.1 and describing application areas for them in Section 3.2. Moreover, an overview of commonly used hardware architectures is given with a focus on the structure and properties of the processor pipelines in Section 3.3.

# 3.1 Overview

According to [Mar05], an embedded system is an information processing system embedded into a larger product. This means that the system itself normally is not directly visible to its user. For example, there are embedded systems within modern cars processing sensor inputs but the driver itself is not aware of them besides some notification icons in the cockpit.

From a historical point of view embedded systems represent the newest of three eras of computer systems:

- ▶ *Mainframe computing systems* mainly used by scientists and large companies have build the starting era until the late eighties.

- ▶ *Personal computing systems* then were introduced during the nineties offering computing power to "everyone".

- ► *Embedded systems* represent the usage of computers within enclosing products of every day life to provide omnipresent information.

As stated by Mark Weiser [Wei95], the growing demand for ubiquitous computing will more and more cause the disappearance of personal computers in favor of the "Internet of Things". This means that smaller and smaller objects which are connected to different networks (like the Internet), simplifies information retrieval.

Technically, an embedded system is not necessarily always decomposed into the actual application code and an underlying operating system. Especially for small systems, the latter might be missing so that the application needs to take care about low-level functionality like the communication to peripheral devices. Otherwise, employed operating systems are typically specialized and have been specifically developed for their purpose [Win, QNX]. But there are also customized versions of standard operating systems like Linux [Lin] and Windows 7 [Mic]. The actual application is often structured into a set of

different processes. If the processes are scheduled by an operating system, they are usually called *tasks*.

# 3.1.1 Characteristics

Embedded systems are designed for specific purposes, so there are different characteristic properties of such systems. The following list presents an overview of such properties. Depending on the concrete application scenario, the importance of the different properties varies which also influences particularly required limits.

**Reliability** The reliability is the likeliness that a system will not fail, i.e., the system does not work as expected. This is often expressed in terms of probabilities.

**Maintainability** The maintainability of a system describes how much effort is needed to keep the system in a working state. This either means to prevent failures by providing regular support as well as the average time to repair a failing system.

**Availability** The availability of a system is the percentage of time when it is in an operational condition and is strongly connected to the reliability and maintainability. Without a high reliability and maintainability, the availability of that system cannot be high.

**Safety** The safety of a system is a metric that measures the probability of the occurrence of a failure that lead to hazards for either human life, property or the system's environment. Safety standards like the ISO 26262 [ISO11] define corresponding limits for these probabilities.

**Security** The security of a system defines whether failures in that system can reveal any confidential data stored in it.

**Efficiency** The efficiency of an embedded system addresses different aspects:

# ► Energy

The power consumption of an embedded system is important especially if the power source is a battery. On the one hand, the computational demands of embedded applications are growing rapidly but on the other hand, the battery technology only increases at a slow rate. So, the power consumption needs to be minimized in order to achieve long runtimes for the systems.

### ► Code size

The executed software needs to be stored within the embedded system. Often the storage capacities are restricted due to size and cost reasons, i.e., because the final system cannot effort to exceed a certain size and more storage capacities increase the production costs. This is also important for so-called systems on a chip (SoCs) integrating all components of a computer or other electronic systems into a single integrated circuit (chip). Storing the instruction memory on that chip raises the requirement to minimize the code size.

# ► Runtime efficiency

This topic covers different aspects:

- ▶ the system only contains the minimum amount of resources or hardware components,

- ▶ the clock frequencies as well as the supply voltage are minimized and

- existing timing constraints must be met.

### **▶** Weight

The weight of the system often needs to be minimized, especially for mobile devices.

### ► Cost

The production costs – especially for high-volume products in consumer electronics – are an important property. Often, these costs decide over the competitiveness of the system compared to similar products of another manufacturer.

The different aspects are not independent of each other and partly counterproductive. For example, reducing the weight of a system can be achieved by smaller batteries. But ignoring possible technological improvements these batteries provide less energy.

**Application** Embedded systems are designed for a single purpose and not for general purpose computing. Once produced, they will work for that purpose during their product life time. The reasons for that principle are simply that the more functions a system provides, the smaller is the dependability, reliability, maintainability, etc. Furthermore, this would have the consequence that resources which are only used for providing one of the multiple functions, often remain unused.