## Symbolic Representations in WCET Analysis

Zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

## Stephan Wilhelm

Saarbrücken, November 2011

#### Dekan:

Prof. Dr. Mark Groves

#### **Prüfungsausschuss:**

(Vorsitzender) Prof. Dr. Sebastian Hack Prof. Dr. Dr. h.c. mult. Reinhard Wilhelm (Gutachter) (Gutachter) Prof. Dr. Bernd Becker Dr. Daniel Grund

## Tag des Kolloquiums:

04.06.2012

# (akademischer Mitarbeiter)

#### Impressum

Copyright © 2012 Stephan Wilhelm Druck und Verlag: epubli GmbH, Berlin, www.epubli.de ISBN: 978-3-8442-2463-4

#### Abstract

Reliable task-level execution time information is indispensable for validating the correct operation of safety-critical embedded real-time systems. Static worst-case execution time (WCET) analysis is a method that computes safe upper bounds of the execution time of single uninterrupted tasks. The method is based on abstract interpretation and involves abstract hardware models that capture the timing behavior of the processor on which the tasks run. For complex processors, tasklevel execution time bounds are obtained by a state space exploration which involves the abstract model and the program. Partial state space exploration is not sound. A full exploration can become too expensive. Symbolic state space exploration methods using binary decision diagrams (BDDs) are known to provide efficient means for covering large state spaces. This work presents a symbolic method for the efficient state space exploration of abstract pipeline models in the context of static WCET analysis. The method has been implemented for the Infineon TriCore 1 which is a real-life processor of medium complexity. Experimental results on a set of benchmarks and an automotive industry application demonstrate that the approach improves the scalability of static WCET analysis while maintaining soundness.

### Zusammenfassung

Zuverlässige Informationen über die Ausführungszeiten von Programmen sind unerlässlich, um das korrekte Verhalten von sicherheitskritischen eingebetteten Echtzeitsystemen zu garantieren. Die statische Analyse der längsten Ausführungszeit, der sogenannten WCET, ist eine Methode zur Berechnung sicherer oberer Schranken der Ausführungszeiten einzelner, nicht unterbrochener Programmtasks. Sie beruht auf der Methode der Abstrakten Interpretation und verwendet abstrakte Modelle, die das Zeitverhalten des Prozessors erfassen, auf dem die Programme ausgeführt werden. Die Berechnung der Ausführungszeitschranken komplexer Prozessoren basiert auf der Exploration eines Zustandsraums, der sowohl das abstrakte Modell, als auch das Programm umfasst. Eine nur teilweise Abdeckung dieses Zustandsraums liefert dabei keine verlässlichen Ergebnisse. Eine vollständige Exploration ist hingegen sehr aufwändig. Symbolische Methoden, die binäre Entscheidungsdiagramme (BDDs) verwenden, sind dafür bekannt, dass sie die effiziente Abdeckung großer Zustandsräume erlauben. Die vorliegende Arbeit stellt eine symbolische Methode zur effizienten Exploration von Zustandsräumen abstrakter Pipelinemodelle im Rahmen der statischen WCET-Analyse vor. Die Methode wurde für einen realen Prozessor mittlerer Komplexität, den Infineon TriCore 1, implementiert. Ergebnisse von Experimenten mit Benchmarks sowie mit einer Anwendung aus dem Automobilbereich zeigen, dass der Ansatz die Skalierbarkeit statischer WCET-Analyse verbessert, wobei die Zuverlässigkeit der berechneten Schranken gewahrt bleibt.

#### **Extended Abstract**

Reliable task-level execution time information is indispensable for validating the correct operation of safety-critical (or hard) embedded real-time systems. Hard real-time systems use static scheduling strategies that fail if a task misses its assigned deadline. Such failures may lead to wholesome system crashes and are therefore unacceptable in a safety-critical context. However, this type of failure can be prevented if the scheduling takes the worst-case execution times (WCETs) of all tasks into account. In practice the WCET of a task cannot be determined exactly for realistic systems. However, upper bounds of the WCET are sufficient for computing safe schedules. Actually determining such bounds is difficult because the execution time of a task depends not only on the executed program code, but also on the potential input values, and on the clock rate of the processor on which the task runs. Modern processors implement features to reduce the average execution time, e.g., pipelines and caches. Execution times on such processors also depend on the execution history and on the start state of the hardware. As a consequence, tools for WCET prediction have to cover all feasible program paths, inputs, and hardware states.

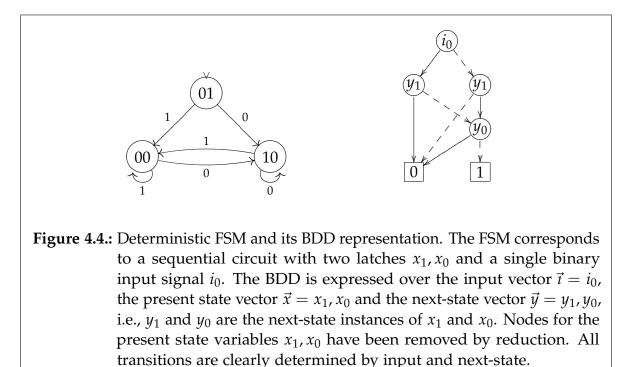

Measurement-based approaches for WCET prediction cannot guarantee full coverage and are prone to miss worst-case situations. In particular, hardware-related timing accidents like pipeline stalls and cache misses can be hard to stimulate but can cause tremendous variations in execution time. In contrast, static WCET analysis can guarantee safe upper bounds of the WCET. The state space of the hardware is covered using abstract cache and pipeline models. The employed pipeline models are finite state machines (FSMs) whose transitions correspond to processor clock cycles. Upper bounds of the execution time of a program can be obtained by counting cycles of the pipeline model. To predict timing accidents, an overapproximation of the set of reachable pipeline and cache states is computed for each program point.

Static WCET analysis only becomes computationally feasible in practice by using abstraction, which is applied to both the modeling of processor and program behavior. However, abstraction loses information which leads to uncertainty, e.g., it may not be possible to statically determine the exact address of a memory access. Furthermore, program inputs are not precisely known in advance. At the level of the pipeline model, this lack of information is accounted for by non-deterministic choices. To be safe, the analysis has to exhaustively explore all reachable states of the FSM. This can lead to state explosion making an explicit enumeration of states infeasible due to memory and computation time constraints. The problem of efficiently covering the state space of large FSMs is well-known in hardware model checking. Only the use of symbolic methods, using Binary Decision Diagrams (BDDs), allowed model checking to be successfully applied for the verification of large, complex hardware models. To this end, symbolic model checking uses an implicit encoding of the transition system and of analysis information, like sets of states in state traversal. This work discusses how the implicit state traversal methods of symbolic model

checking can be used for static WCET analysis to allow for a more efficient handling of abstract pipeline models. Static WCET analysis only scales to realistic programs and hardware models because it carefully separates the problem of WCET prediction into several easier sub-problems. The symbolic implementation of pipeline analysis must therefore exchange results with other analyses that use different abstract representations. We show how this exchange of information can be implemented in an efficient way. Symbolic pipeline analysis also faces the specific problem that it considers the combined state space of a hardware and software model. This sets it apart from hardware and software model checking which only address hardware or software, respectively. However, symbolic methods are very sensitive with regard to the size of the model. A combined hard- and software model is huge and a symbolic analysis of such a model may therefore be inefficient. This work presents a method for decomposing the software under analysis without compromising the soundness of the approach. The decomposition allows to analyze parts of the software individually using smaller, more efficient models. Analysis information, i.e., sets of pipeline states, is translated between program parts using symbolic computations. Finally, interfacing a non-symbolic cache analysis is particularly difficult because of the interdependence between pipeline and cache. We show a way for solving this interface problem efficiently.

The described symbolic pipeline domain for static WCET analysis has been implemented in a commercial WCET tool. We present the general structure of the implementation and describe the model of the Infineon TriCore 1, an embedded processor of medium complexity that is commonly used for safety-critical applications in the automotive industry. The implementation has been evaluated using benchmark programs and an industrial automotive software for engine control. The results demonstrate that the symbolic implementation of pipeline domains improves the scalability of static WCET analysis.

## Erweiterte Zusammenfassung

Zuverlässige Informationen über die Ausführungszeiten von Programmen sind unerlässlich, um das korrekte Verhalten von sicherheitskritischen (harten) eingebetteten Echtzeitsystemen zu garantieren. Harte Echtzeitsysteme verwenden statische Verfahren zur Ablaufplanung. Diese Verfahren versagen jedoch, wenn eine Task die ihr zugewiesene Zeitschranke überschreitet. Solche Fehler können zu kompletten Systemabstürzen führen und sind daher in einem sicherheitskritischen Kontext inakzeptabel. Es ist jedoch möglich, diese Art von Fehler zu vermeiden, indem man bei der Ablaufplanung die längsten Ausführungszeiten (WCETs) aller Tasks berücksichtigt. In der Praxis ist die genaue Ermittlung der WCET eines realistischen Programms nicht möglich, jedoch sind obere Schranken der Ausführungszeit hinreichend für die Berechnung sicherer Ablaufpläne. Die tatsächliche Bestimmung solcher Schranken ist allerdings schwierig, da die Ausführungszeit nicht nur vom Programm selbst, sondern auch von den möglichen Eingabewerten und der Taktfrequenz des ausführenden Prozessors abhängt. Moderne Prozessoren reduzieren die durchschnittliche Ausführungszeit mit Hilfe von Caches und Pipelines. Bei solchen Prozessoren hängt die Ausführungszeit auch von der Ausführungsgeschichte und dem Ausgangszustand der Hardware ab. Daher müssen Werkzeuge zur Vorhersage der WCET alle zulässigen Programmpfade, Eingaben und Hardwarezustände abdecken.

Messbasierte Verfahren zur Vorhersage der WCET können keine vollständige Abdeckung garantieren und berücksichtigen häufig nicht den schlimmsten Fall. Insbesondere Verzögerungen, die durch Hardwareeffekte ausgelöst werden, beispielsweise ein zeitweises Anhalten der Pipeline oder Zugriffe auf Daten, die sich nicht im Cache befinden, können in Messungen nur schwer stimuliert werden. Solche Effekte können jedoch zu erheblichen Varianzen der Ausführungszeit führen. Im Gegensatz zu messbasierten Verfahren liefert die statische WCET-Analyse sichere obere Ausführungszeitschranken. Der Zustandsraum der Hardware wird dabei mit Hilfe abstrakter Cache- und Pipelinemodelle abgedeckt. Die dazu verwendeten Pipelinemodelle sind endliche Automaten (FSMs), deren Übergänge Prozessorzyklen entsprechen. Obere Ausführungszeitschranken eines Programms erhält man durch Zählen der Zyklen im Pipelinemodell. Zur Vorhersage hardwarebedingter Verzögerungen wird eine Überapproximation der möglichen Pipeline- und Cachezustände für jeden Programmpunkt berechnet.

Statische WCET-Analysen werden erst durch Abstraktionen auf der Ebene des Prozessormodells und des Programmverhaltens praktisch berechenbar. Solche Abstraktionen sind mit einem Informationsverlust verbunden, der zu Unschärfen in der Analyse führt. So ist es beispielsweise nicht immer möglich, die genaue Adresse eines Speicherzugriffs statisch zu bestimmen. Desweiteren sind Programmeingaben im Vorhinein ebenfalls nicht genau bekannt. Auf der Ebene des Pipelinemodells werden solche Ungenauigkeiten durch nicht-deterministische Übergänge behandelt. Um ein sicheres Ergebnis zu erhalten, muss die Analyse die erreichbaren FSM-Zustände vollständig abdecken. Die erreichbare Zustandsmenge kann dabei so groß werden (Stichwort Zustandsexplosion), dass eine explizite Aufzählung aller Zustände aufgrund von Speicherplatz- und Berechnungszeitlimits unmöglich wird. Die effiziente Abdeckung von Zustandsräumen großer FSMs ist ein bekanntes Problem aus dem Bereich des Hardware Model Checking. Erst durch die Verwendung symbolischer Methoden, basierend auf binären Entscheidungsdiagrammen (BDDs), ist es gelungen, komplexe Hardwaremodelle erfolgreich durch Model Checking zu verifizieren. Symbolisches Model Checking verwendet dabei eine implizite Darstellung, sowohl des Transitionssystems, als auch von Analyseinformation wie z.B. Mengen von Zuständen.

Die vorliegende Arbeit zeigt, wie implizite Explorationsmethoden aus dem Bereich des symbolischen Model Checking in der statischen WCET-Analyse eingesetzt werden können, um eine effizientere Behandlung abstrakter Pipelinemodelle zu ermöglichen. Statische WCET-Analyse skaliert nur deshalb auf realistische Programme und Hardwaremodelle, weil sie das Problem der WCET-Vorhersage in mehrere, jeweils einfachere, Teilprobleme zerlegt. Die symbolische Implementierung der Pipelineanalyse muss daher Informationen mit anderen Analysen austauschen, die andere abstrakte Darstellungen verwenden. In der vorliegenden Arbeit wird gezeigt, wie dieser Informationsaustausch auf effiziente Weise implementiert werden kann. Die symbolische Pipelineanalyse steht auch vor dem speziellen Problem, dass sie den kombinierten Zustandsraum eines Hard- und Softwaremodells betrachtet. Damit unterscheidet sie sich von Hardware und Software Model Checking, welches jeweils nur die Hardware oder die Software untersucht. Leider reagieren symbolische Methoden sehr empfindlich auf die Modellgröße. Da ein kombiniertes Hard- und Softwaremodell sehr groß ist, kann die symbolische Analyse eines solchen Modells ineffizient sein. Die vorliegende Arbeit zeigt eine Methode zur Zerlegung der analysierten Software, wobei die Zuverlässigkeit der Analyseergebnisse gewahrt bleibt. Die Zerlegungsmethode erlaubt es, Teile der Software mit kleineren Modellen effizienter zu analysieren. Die Analyseinformation, d.h. Mengen von Pipelinezuständen, wird zwischen den Programmteilen mit Hilfe symbolischer Berechnungen übersetzt. Schließlich bleibt das Problem der Kopplung mit einer nicht-symbolischen Cacheanalyse, welches aufgrund der wechselseitigen Abhängigkeit zwischen Pipeline und Cache besonders schwer zu lösen ist. Eine effiziente Lösung dieses Kopplungsproblems wird ebenfalls vorgestellt.

Die vorgestellte symbolische Pipelineanalyse wurde im Rahmen eines kommerziellen Analysewerkzeugs zur statischen WCET-Vorhersage implementiert. Diese Arbeit zeigt auch den allgemeinen Aufbau der Implementierung und beschreibt das Modell des Infineon TriCore 1, eines eingebetten Prozessors mittlerer Komplexität, der in sicherheitskritischen Anwendungen in der Automobilindustrie weit verbreitet ist. Die Implementierung wurde auf Benchmarkprogrammen und einer Automobilanwendung zur Motorsteuerung evaluiert. Die Ergebnisse belegen, dass die symbolische Implementierung der Pipelineanalyse die Skalierbarkeit statischer WCET-Analysen verbessert.

## Acknowledgments

First of all, I would like to thank my advisor Prof. Reinhard Wilhelm for his invaluable advice and continuous support over the last couple of years. He gave me enough freedom to let me find my way and enough guidance to get this thesis finished.

My best thanks also go to the other members of my committee: Prof. Bernd Becker, Prof. Sebastian Hack, and Dr. Daniel Grund for taking the time to review this thesis and for taking part in the defense session.

Moreover, I am grateful for the support of many people at AbsInt GmbH and at the Compiler Design Lab at Saarland University. Christian Ferdinand allowed me to dedicate some of my working time at AbsInt to research. Daniel Kästner and Reinhold Heckmann both did an excellent job of patiently proof reading several versions of the manuscript. Björn Wachter and Christoph Cullmann had a part in getting the results of this work published at international workshops and conferences. Florian Martin, Michael Schmidt, and Henrik Theiling introduced me to the depths of AbsInt's static WCET analysis tool chain. Frank Fontaine, Gernot Gebhard, Markus Pister, Marc Schlickling, and Ingmar Stein shared with me their knowledge of pipeline models. Thanks also to Nicolas Fritz, Christian Hümbert, Marc Langenbach, Philipp Lucas, Stefana Nenova, Martin Sicks, and Stephan Thesing for their support and for contributing to a pleasant working atmosphere. I sincerely apologize for having forgotten to mention anyone to whom acknowledgment is due. Rest assured that I am grateful for every bit of support and encouragement that I ever got.

Finally, I would like to thank my family and friends. Their love and support helped me to keep up the motivation for this long-term project. The most special thanks go to my parents Rita and Heribert and – last but not least – to my wife Nicole.

- For Ronja, who has changed my life. -

## Contents

| 1. | Introduction                        |                           |                                         |    |  |  |  |  |  |  |

|----|-------------------------------------|---------------------------|-----------------------------------------|----|--|--|--|--|--|--|

|    | 1.1.                                | WCET                      | Analysis for Hard Real-Time Systems     | 1  |  |  |  |  |  |  |

|    | 1.2.                                |                           | d Work and Contribution                 | 3  |  |  |  |  |  |  |

|    | 1.3.                                | Overv                     | iew                                     | 5  |  |  |  |  |  |  |

| 2. | Related Work 7                      |                           |                                         |    |  |  |  |  |  |  |

|    | 2.1.                                | Schedu                    | ulability, WCRT Analysis, and Compilers | 7  |  |  |  |  |  |  |

|    | 2.2.                                | Deterr                    | nining Task-Level WCET Bounds           | 9  |  |  |  |  |  |  |

|    |                                     | 2.2.1.                    | Dynamic Methods                         | 9  |  |  |  |  |  |  |

|    |                                     | 2.2.2.                    | Static Methods                          | 10 |  |  |  |  |  |  |

|    | 2.3.                                | Symbo                     | olic Methods in WCET Analysis           | 14 |  |  |  |  |  |  |

| 3. | Abst                                | Abstract Interpretation 1 |                                         |    |  |  |  |  |  |  |

|    | 3.1.                                | Lattice                   | e Theory                                | 18 |  |  |  |  |  |  |

|    |                                     |                           |                                         | 19 |  |  |  |  |  |  |

|    | 3.2.                                | Collec                    | ting Semantics                          | 20 |  |  |  |  |  |  |

|    |                                     |                           | •                                       | 23 |  |  |  |  |  |  |

|    | 3.3.                                |                           |                                         | 25 |  |  |  |  |  |  |

| 4. | Symbolic State Space Exploration 29 |                           |                                         |    |  |  |  |  |  |  |

|    | -                                   |                           |                                         | 30 |  |  |  |  |  |  |

|    | 4.2.                                |                           | 6                                       | 31 |  |  |  |  |  |  |

|    |                                     |                           |                                         | 32 |  |  |  |  |  |  |

|    |                                     | 4.2.2.                    |                                         | 34 |  |  |  |  |  |  |

|    |                                     | 4.2.3.                    |                                         | 35 |  |  |  |  |  |  |

|    |                                     | 4.2.4.                    | Dynamic Reordering                      | 36 |  |  |  |  |  |  |

|    | 4.3.                                | Seque                     |                                         | 37 |  |  |  |  |  |  |

|    |                                     | 4.3.1.                    |                                         | 38 |  |  |  |  |  |  |

|    |                                     | 4.3.2.                    |                                         | 39 |  |  |  |  |  |  |

| 5. | Static Worst-Case Execution Time Analysis 41 |                      |                                                        |     |  |  |  |

|----|----------------------------------------------|----------------------|--------------------------------------------------------|-----|--|--|--|

|    | 5.1.                                         | A Fran               | mework for Static WCET Analysis                        | 42  |  |  |  |

|    |                                              | 5.1.1.               | CFG Reconstruction                                     | 43  |  |  |  |

|    |                                              | 5.1.2.               | Value and Control Flow Analyses                        | 43  |  |  |  |

|    |                                              | 5.1.3.               | Microarchitectural Analysis                            | 44  |  |  |  |

|    |                                              | 5.1.4.               | Path Analysis                                          | 45  |  |  |  |

|    |                                              | 5.1.5.               | Abstractions and the Loss of Precision                 | 45  |  |  |  |

|    | 5.2.                                         | Pipeli               | ne Domains                                             | 46  |  |  |  |

|    |                                              | 5.2.1.               | Concrete Semantics                                     | 47  |  |  |  |

|    |                                              | 5.2.2.               | Abstraction                                            | 51  |  |  |  |

|    |                                              | 5.2.3.               | Abstract Semantics                                     | 53  |  |  |  |

|    |                                              | 5.2.4.               | WCET Bounds for Basic Blocks                           | 54  |  |  |  |

|    | 5.3.                                         | The St               | tate Explosion Problem                                 | 55  |  |  |  |

|    |                                              | 5.3.1.               | State Explosion in WCET Analysis                       | 55  |  |  |  |

|    |                                              | 5.3.2.               | Timing Anomalies and Domino Effects                    | 57  |  |  |  |

|    |                                              | 5.3.3.               | The Need for More Efficient Pipeline Domains           | 57  |  |  |  |

| 6. |                                              |                      | Representation of Pipeline Domains                     | 61  |  |  |  |

|    | 6.1.                                         | Consi                | dered Hardware Features                                | 62  |  |  |  |

|    | 6.2.                                         | Basic S              | Symbolic Representation                                | 62  |  |  |  |

|    |                                              | 6.2.1.               | Representation of Pipeline Models                      | 63  |  |  |  |

|    |                                              | 6.2.2.               | Program Representation                                 | 64  |  |  |  |

|    |                                              | 6.2.3.               | Generating the Transition Relations                    | 65  |  |  |  |

|    | 6.3.                                         | Symbo                | olic Computation of Abstract Traces                    | 69  |  |  |  |

|    |                                              | 6.3.1.               | Integration with a Data Flow Analysis Framework        | 71  |  |  |  |

|    | 6.4.                                         | Scalin               | g to Realistic Pipeline Models and Programs            | 73  |  |  |  |

|    |                                              | 6.4.1.               | Conjunctive Partitioning                               |     |  |  |  |

|    |                                              | 6.4.2.               | Address and Context Compression                        |     |  |  |  |

|    |                                              | 6.4.3.               | Processor-Specific Optimizations                       | 75  |  |  |  |

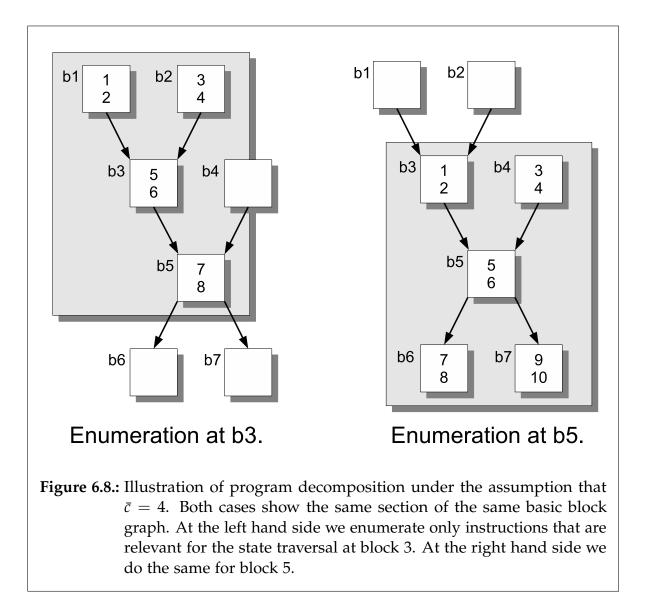

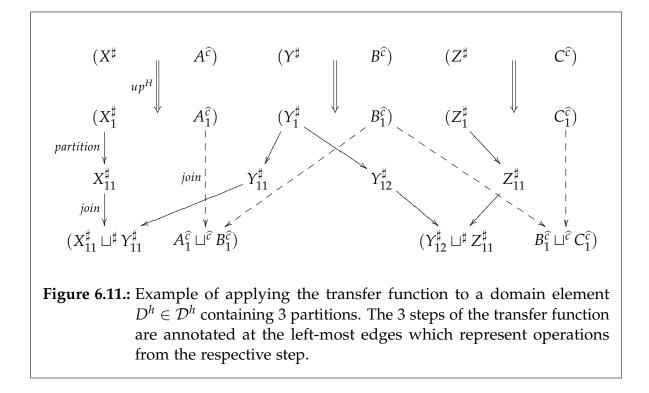

|    |                                              | 6.4.4.               | Program Decomposition                                  | 78  |  |  |  |

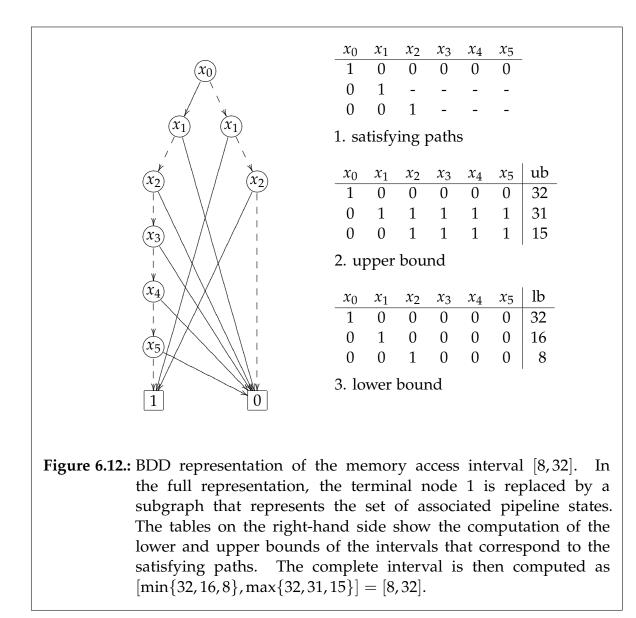

|    | 6.5.                                         | Interfa              | acing Abstract Caches                                  | 83  |  |  |  |

|    |                                              | 6.5.1.               | The Interface Problem                                  | 84  |  |  |  |

|    |                                              | 6.5.2.               | A Semi-Symbolic Domain for Microarchitectural Analysis | 84  |  |  |  |

|    |                                              | 6.5.3.               | State Traversal and Performance                        | 88  |  |  |  |

|    | 6.6.                                         | Summ                 | nary                                                   | 91  |  |  |  |

| 7. | Prac                                         | actical Evaluation 9 |                                                        |     |  |  |  |

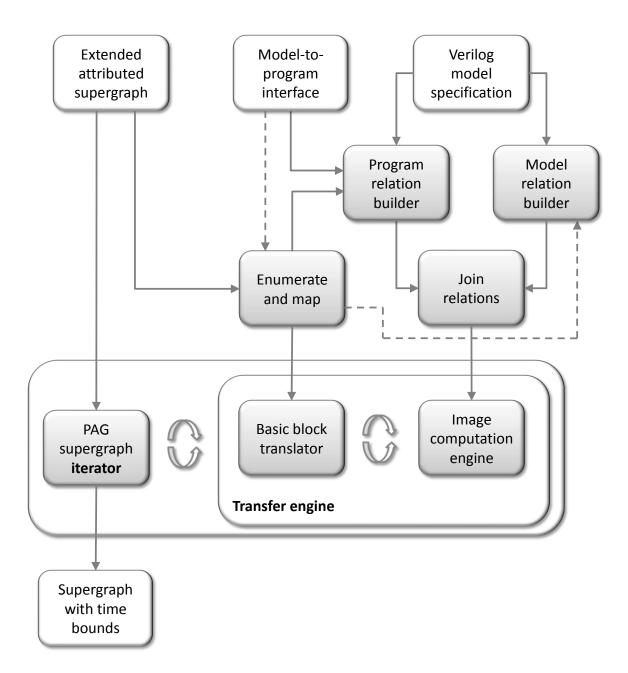

|    | 7.1.                                         | A Fra                | mework for Symbolic Pipeline Analyses                  | 94  |  |  |  |

|    |                                              | 7.1.1.               | Enumerate and Map                                      | 96  |  |  |  |

|    |                                              | 7.1.2.               | The Model Relation Builder                             | 98  |  |  |  |

|    |                                              | 7.1.3.               | The Program Relation Builder                           | 99  |  |  |  |

|    |                                              | 7.1.4.               | Iterator, Transfer Function, and Control Flow Handling | 99  |  |  |  |

|    |                                              | 7.1.5.               | Debugging Interface                                    | 100 |  |  |  |

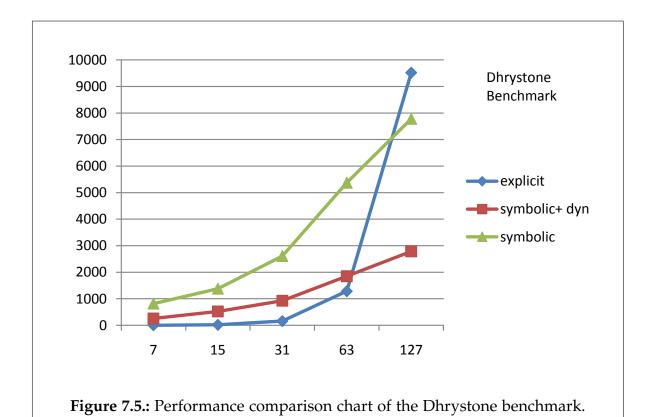

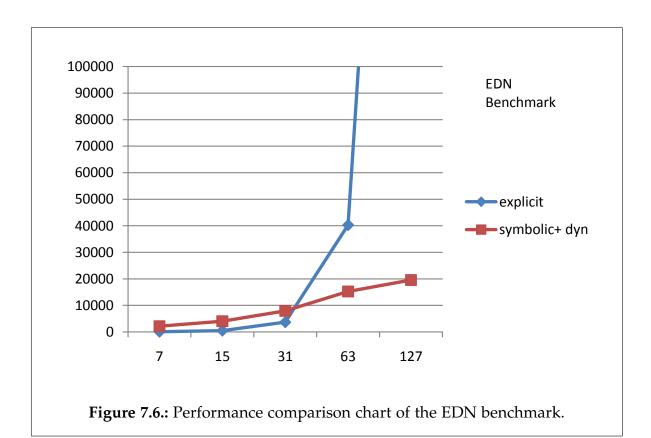

|              | 7.2.               | Experi                              | mental Results                       | . 100 |  |  |  |  |  |

|--------------|--------------------|-------------------------------------|--------------------------------------|-------|--|--|--|--|--|

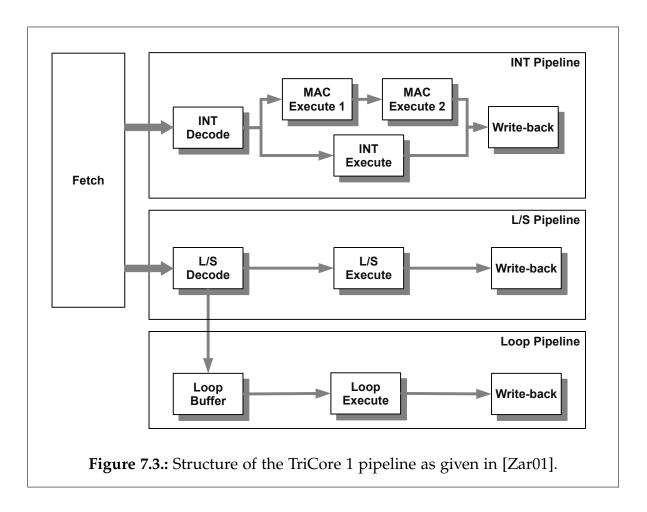

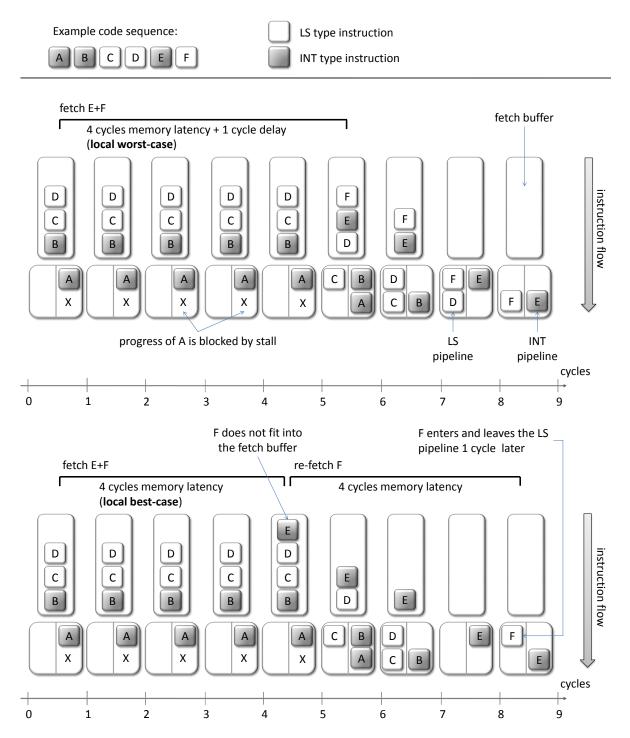

|              |                    | -                                   | The Infineon TriCore 1               |       |  |  |  |  |  |

|              |                    | 7.2.2.                              | A Timing Anomaly Example             | . 103 |  |  |  |  |  |

|              |                    | 7.2.3.                              | TriCore 1 Pipeline Models            |       |  |  |  |  |  |

|              |                    | 7.2.4.                              |                                      |       |  |  |  |  |  |

|              |                    | 7.2.5.                              | _                                    |       |  |  |  |  |  |

|              | 7.3.               | Lessons Learned from Implementation |                                      | . 120 |  |  |  |  |  |

|              |                    | 7.3.1.                              | Dealing with the Non-Determinism     | . 121 |  |  |  |  |  |

|              |                    | 7.3.2.                              | Debugging and Pipeline State Graphs  | . 121 |  |  |  |  |  |

|              | 7.4.               |                                     | ary                                  |       |  |  |  |  |  |

| 8.           | Con                | onclusion                           |                                      |       |  |  |  |  |  |

|              | 8.1.               | Result                              | s and Contribution                   | . 126 |  |  |  |  |  |

|              | 8.2.               | Indust                              | rial Application and Future Research | . 128 |  |  |  |  |  |

|              |                    | 8.2.1.                              | Hybrid Pipeline Analyzers            | . 129 |  |  |  |  |  |

|              |                    | 8.2.2.                              | Alternative Symbolic Representations | . 129 |  |  |  |  |  |

|              |                    | 8.2.3.                              | Scaling to Larger Pipeline Models    | . 130 |  |  |  |  |  |

|              | 8.3.               | Outloo                              | ok                                   | . 131 |  |  |  |  |  |

| Α.           | . Fetch unit model |                                     |                                      |       |  |  |  |  |  |

|              | A.1.               | Unit T                              | ransition Rules                      | . 134 |  |  |  |  |  |

|              | A.2.               | Progra                              | m Interface                          | . 140 |  |  |  |  |  |

| Bibliography |                    |                                     |                                      |       |  |  |  |  |  |

| Index        |                    |                                     |                                      |       |  |  |  |  |  |

## CHAPTER 1

## Introduction

## 1.1. WCET Analysis for Hard Real-Time Systems

Over the last two decades, computers have found their way into many objects of daily life, including some whose origins precede the computer era. Cars are a very good example. In the seventies of the last century, an automotive engine wasn't much more than four cylinders powering a driveshaft. Today, all modern engines use a computer for precise control of the engine speed, temperature, and the injection pump, in order to reduce fuel consumption, and to fulfill emission standards. Such computers, together with the software that is running on them, are known as *embedded systems*. They are not only in cars; modern airplanes, cell phones, and portable MP3 players also rely on embedded computers – and *rely* means that they will not work properly if the embedded system fails. People may not care much if their MP3 player chokes on some particular track or if their cell phone breaks down in the middle of an unpleasant conversation. But a person who is sitting in an airplane that approaches the runway with landing speed wants to be sure that all relevant embedded systems in the plane are working correctly. Therefore, many embedded systems in airplanes and cars are considered to be safety-critical - lives may depend on their proper operation.

Safety-critical embedded systems obviously have to satisfy high quality requirements. For example, the flight control system of an airplane should never perform a division by zero which would halt the processor. Many embedded systems are also critical with respect to the execution time; e.g., an engine control system must perform its computations fast enough, even if the engine is running at full speed. Embedded systems with execution time constraints are termed *real-time* embedded systems. Systems with execution time constraints that are safety-critical are called *hard* real-time systems. For these systems, one must not only prove the absence of critical run-time errors – like division by zero – but also ensure that the system always reacts

in-time. The question is: how can such properties be proved? In the past, engineers verified the safety of their constructions by testing; either by putting critical loads onto their construction, or by running long-term tests. For mechanical systems, this approach is still valid, although it is increasingly replaced by computer simulation for reasons of cost. However, for safety-critical embedded systems, testing is no longer sufficient because of two reasons: the state space of the embedded soft- and hardware is too large to admit an adequate test coverage, and second, it is usually not possible to choose a limited set of inputs that stimulates the critical executions. This problem is well-known in computer science; it is equivalent to the insight that all interesting questions about the concrete semantics of a program are undecidable. A solution for answering – at least some – questions about the undecidable semantics of a program exists in the form of abstract interpretation. A sound abstract interpretation is a static analysis that replaces the undecidable concrete semantics by abstract semantics that over-approximate any concrete execution. The gained computability is paid for by a loss of precision; the analysis may consider spurious executions that do not correspond to any concrete execution. However, abstract interpretation is also exhaustive, i.e., it never misses a possible execution, and therefore provides full coverage over all inputs and execution paths. These two properties - incompleteness and full coverage - are often summarized by the statement that abstract interpretation only errs on the safe side. Hence, abstract interpretation can be used to prove properties of software. Static analysis tools based on abstract interpretation recently found their way into the mainstream avionics and automotive industry and are now considered to provide state-of-the-art solutions for the verification of safety-critical, embedded real-time systems. As such, their use is increasingly encouraged by certification authorities, particularly in the civil avionics industry, where the certification standard DO-178B [Rad] requires the use of state-of-the-art technologies to prove the absence of errors in safety-critical systems. A good example of a static analysis tool that is used in the avionics industry is the Astrée static analyzer. Astrée can be used to prove the absence of certain run-time errors - such as division by zero, invalid pointer dereference, or array out-of-bound accesses - on synchronous command-andcontrol programs, written in ANSI C. Synchronous command-and-control programs consist of a main loop that controls the execution of system tasks using a static schedule. They are often found in safety-critical embedded real-time systems, such as the flight-control system of an aircraft. Obviously, the proper operation of such a system not only requires that it is free of run-time errors, but also that each task meets its deadline.

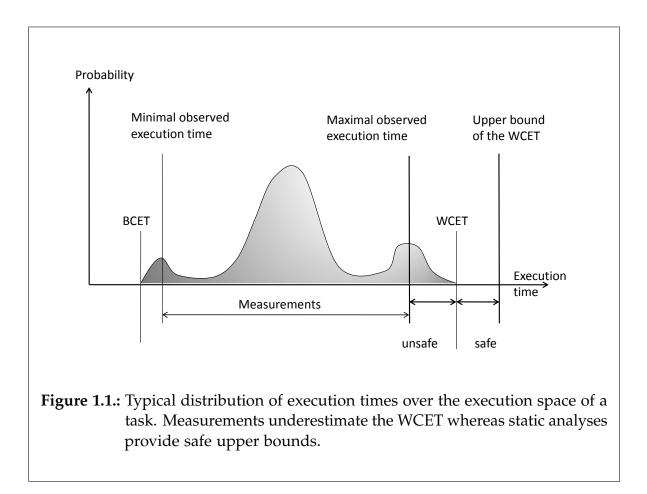

The problem of giving guarantees about the timeliness of a task is known as *worst-case execution time* prediction, or WCET prediction, for short. Because of the already mentioned lack of coverage, measurements – which are the equivalent of testing for WCET prediction – are not an option when it comes to hard, i.e., safety-critical, real-time systems. The inadequacy of measurements for the purpose of WCET prediction is visualized by Figure 1.1. Taking measurements means taking samples from the set of possible executions. In this set, the variance is usually large and the values are not evenly distributed. This is partly because of the range of inputs and

different operating modes but also because the execution time of modern hardware, featuring caches and complex pipelines, is very sensitive with respect to the start state and execution history [HLTW03, Rei08]. There is only little chance for observing unusually small or high execution times. Even worse, virtually all observed values *underestimate* the worst-case, i.e., measurements err on the unsafe side. Because the difference between the worst-case measurement and the actual worst-case is unknown, adding "safety" margins to account for underestimations, is not safe; and even if the results overestimate the worst-case, they are often not precise enough. For the analysis of single, uninterrupted tasks, static WCET analysis is a safe alternative. It provides full coverage and computes *upper bounds* on the execution time that hold for all possible executions.

## 1.2. Related Work and Contribution

Research on formal verification methods usually falls into one of the following categories: abstract interpretation, model checking, and theorem proving. Model checking and theorem proving have been successfully used for hardware verification [JM01, CGH<sup>+</sup>93, CRSS94] and there have been efforts to integrate both methods

[Ber02]. In contrast, abstract interpretation originates from the area of software verification where it is successfully used, e.g., to prove the absence of run-time errors [BCC<sup>+</sup>03]. Despite recent attempts to use model checking for software verification [BHJM07, BLQ<sup>+</sup>03, WL04] there has been little exchange between the two communities.

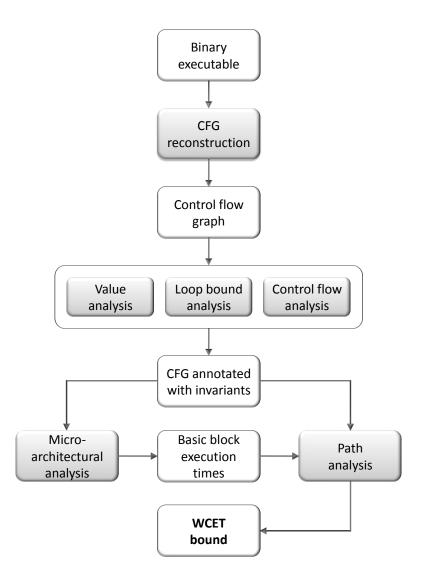

Static WCET analysis is an area that has contact points with both, hardware and software verification. A major research effort for static WCET tools has been made by Reinhard Wilhelm's group at Saarland University. They tackled the problem from the software-oriented perspective of abstract interpretation, and developed an approach that decomposes the task into several sub-problems [FHL<sup>+</sup>01, HLTW03]. Each sub-problem is solved by a dedicated analysis. Abstract hardware models of the cache and the pipeline are used to predict low-level timing effects [Fer97, The04]. The computation of the worst-case program path is based on integer linear programming [The02]. While this approach is nowadays well-established in industry [TSH<sup>+</sup>03, WEE<sup>+</sup>08], the use of model checking for WCET analysis has been a subject of controversial discussion between researchers.

Early work on model checking for static WCET analysis focused on synchronous programs, assuming a single-cycle execution model [LS03, LSM03]. This execution model does not hold for modern processor hardware using pipelined execution and caches to improve the average execution time. More recent research takes the timing effects of the hardware into account [DOT<sup>+</sup>10], but so far addresses only the most simple pipelines, cannot handle floating-point computations, and suffers from scalability problems. At the same time, WCET tools based on abstract interpretation analyze industrial-level software, running on complex, superscalar pipelines with caches. Thus, it seems that there is a tremendous gap between model checking and abstract interpretation when it comes to WCET analysis. In 2004, Reinhard Wilhelm published a paper that discusses the challenges that model checking faces in WCET analysis [Wil04]. His major argument is still not disproved: the combined state space of program paths, variable values, pipeline, and cache state is too large to admit an exhaustive traversal without using dynamic abstraction. The reply by Metzner [Met04] misses the point when he discusses the imprecisions in abstract cache analysis [Fer97], and proposes improvements by model checking. Abstract interpretation deliberately loses precision to gain computability, and experimental results show that the computed WCET bounds are tight enough in practice [TSH<sup>+</sup>03, SLH<sup>+</sup>05].

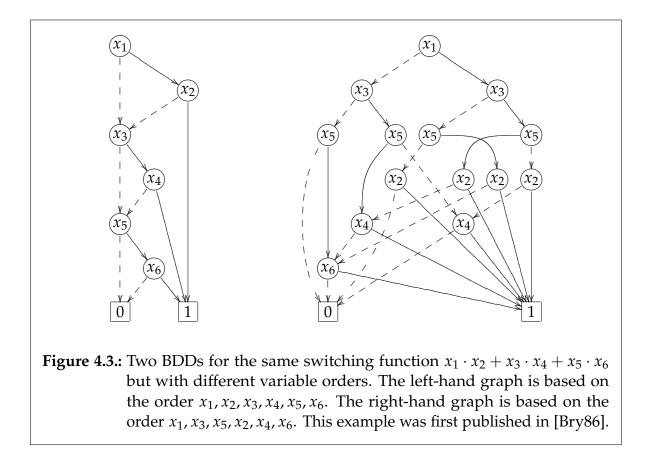

Despite its undeniable success, static WCET analysis based on abstract interpretation sometimes runs into problems at its contact points with hardware verification. In particular, the analysis of the pipeline timing requires an exhaustive traversal of the reachable state space of the pipeline model; for pipelines with large state spaces, the analysis can become infeasible [The04]. The problem of state explosion is well-known in model checking. Symbolic representations, usually based on binary decision diagrams [Bry86], have significantly improved the situation because they admit both an implicit encoding of the transition system and of analysis information like sets of states in state traversal [McM92]. This has enabled the analysis of hardware designs

with large state spaces [BCM<sup>+</sup>90]. Although model checking alone may not be the adequate approach for WCET prediction, some of its methods can be exploited to improve static WCET analysis.

The research that is presented here focuses on improving the efficiency of pipeline analysis in cases where large sets of pipeline states have to be considered. To this end, Chapter 6 presents a novel approach for implementing pipeline analysis using a symbolic representation. The approach combines ideas from the world of model checking with the advantages of static program analysis based on abstract interpretation. Chapter 7 describes the implementation of a framework for symbolic pipeline analyses and a pipeline model of the Infineon TriCore 1 [AG08, Zar01]. Experimental results that have been obtained with this model show that the approach is indeed more efficient in practically relevant scenarios. A summary of the two chapters has been published in [WW09].<sup>1</sup> The integration with cache analysis has been published in [WC10]. Further contributions are found in Section 5.2 and Section 7.3. Section 5.2 gives a more profound presentation of pipeline analysis than what is found in overview publications like [FHL<sup>+</sup>01]. At the same time, the description and the given proof of soundness are more general than the presentation in [The04], which describes the pipeline model of a specific processor and proves its correctness. The state explosion problem in WCET analysis, which has first been mentioned in [The04], is discussed in detail since it represents the motivation for the use of symbolic methods. Finally, Section 7.3 discusses several practical consequences that arise from the use of symbolic methods for pipeline analysis. These insights have not been published before.

## 1.3 Overview

This work is structured into 8 chapters, including this introduction. Here is an overview of the contents of the remaining chapters:

*Chapter 2* gives an overview of WCET analysis including various system-level and task-level analysis methods. We discuss the existing research and show how task-level and system-level analyses interact.

*Chapter 3* presents the fundamentals of static program analysis. It discusses the design of abstract domains for static analyses, the actual computation of semantic invariants, and the underlying theory of abstract interpretation.

*Chapter 4* gives a similarly fundamental introduction into symbolic state traversal for sequential circuits. It comprises a discussion of binary decision diagrams as a data structure for the compact representation of Boolean functions.

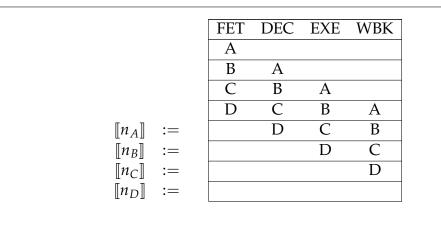

*Chapter 5* presents the general design of static analysis tools for computing upper bounds on the execution time of tasks. It shows how the problem can be decomposed into several analyses and how these analyses interact. Pipeline domains based on abstract hardware models are discussed in detail.

<sup>&</sup>lt;sup>1</sup>The idea first appeared in [Wil05]. Intermediate results were published in [WW07].

*Chapter 6* shows how pipeline domains can be represented symbolically using binary decision diagrams. Further, it details how such a domain can be integrated with a framework for static WCET analysis.

*Chapter* 7 describes the implementation of a framework for symbolic pipeline analyses, and the implementation of a model of the Infineon TriCore 1. Several experiments that compare the performance of the symbolic implementation with a semantically equivalent explicit-state implementation are reported. Further experiments with the pipeline model of the Motorola/Freescale MPC 755 study the efficiency of the cache analysis integration. The chapter is concluded by an experience report about practical implications of the approach.

*Chapter 8* summarizes the achievements of this work. Finally, we give advice regarding the application of the approach in commercial industrial-strength WCET analyzers and propose topics for future research that could lead to further improvements of our method.

## chapter 2

## Related Work

The question of giving guarantees about the worst-case execution times of software has been around for more than 20 years. Since then, the interest in this matter has continuously increased. Notably the advent of safety-critical embedded real-time systems, like fly-by-wire in civil avionics, led to intensified research efforts. This research has been conducted on two levels: the task level and the system level. Task-level WCET bounds are used as inputs for tools that determine properties on the system level, most prominently schedulability and worst-case response time (WCRT) guarantees. The following overview of related work focuses on task-level WCET analysis because that part is directly related to the subject of this thesis. We present a number of approaches and discuss their advantages as well as drawbacks. Existing uses of symbolic methods in WCET analysis are also covered. To set the scene, we begin with a brief description of the three major applications that use task-level WCET information: schedulability tests, WCRT analysis, and WCET-aware compilers.

## 2.1. Schedulability, WCRT Analysis, and Compilers

The software of embedded systems is usually composed of several tasks. Each task implements a sub-function of the system and has to be executed periodically. The period that is assigned to each task depends on the characteristics of the controlled physical system, e.g., the sample rate of a sensor. For the correct operation of the whole software the tasks may have to be executed in a certain order. The execution of each task may also be subject to further constraints, e.g., a task may only run after a certain point in time, or it must finish execution before a certain point in time. The latter constraint is called the task's *deadline*. Executing embedded software in a correct manner that respects its execution constraints and the dependencies between

its tasks is a *scheduling* problem. The task schedule determines the order in which the tasks run.

The computation of task schedules is based on the notion of *priorities*. Each task is assigned a priority such that these priorities establish a total order on the set of tasks. From the set of tasks that are *ready*, i.e., that have no more unfulfilled dependencies, the scheduler selects the highest priority task to execute next. The priority of a task may either be fixed, or determined at run-time based on certain conditions. An example of a strategy for assigning fixed priorities is *rate monotonic* scheduling [LL73]. It determines the priorities of tasks by the lengths of their periods. The task with the smallest period is assigned the highest priority An example of a dynamic scheduling strategy is called *earliest deadline first* [Liu00]. It assigns the highest priority to the task with the nearest deadline. Safety-critical embedded systems usually rely on static schedules that are computed offline based on fixed scheduling strategies.

A schedule that has been computed by a given strategy, either fixed or dynamic, is called feasible if it respects all constraints and dependencies between the tasks. All scheduling strategies guarantee that a feasible schedule can be computed if certain conditions are fulfilled. The satisfaction of these conditions can be checked by a so-called *schedulability test* [BW90, Liu00]. These schedulability tests require information about the *worst-case execution time* (WCET) of all tasks. Hence, the knowledge of upper bounds on the WCET of all tasks of a real-time system is crucial to prove its correct operation.

WCET bounds for tasks are also required to obtain *worst-case response times* (WCRTs) of entire real-time systems. WCRTs can be computed by so-called *system-level* timing analysis tools, e.g., SymTA/S [HHJ<sup>+</sup>05]. Beside task-level WCET bounds, these tools also take information about possible interrupts and their priorities into account. The WCRT can either be computed on the level of a single application running on one microprocessor, or on the network-level if considering embedded systems that are composed of several interacting applications running on multiple processors that are connected by a bus using protocols like CAN [ISO04] or FlexRay [Alt01].

In contrast to the class of schedulability tests and WCRT analysis tools that we discussed so far, Bernat et al. propose probabilistic methods for obtaining schedulability and response time guarantees [BCP02, BBB03]. These methods are convenient for soft real-time systems where safe WCET bounds are not required. They are not suited for safety-critical hard real-time systems because they are neither safe nor sound.

WCET-aware compilers are another, more recent, class of applications that rely on task-level WCET bounds [Fal09, LM09]. The idea is to use WCET information for guiding compilation strategies that reduce the worst-case instead of the average-case execution time. An example of such a tool is the WCC compiler infrastructure [FL10]. It implements a feedback loop with the aiT WCET tool [Abs00] in order to evaluate the WCET effect of already performed optimizations and to asses further optimization potential from the WCET bounds of individual basic blocks and routines.

## 2.2. Determining Task-Level WCET Bounds

It is generally not possible to predict execution times for programs since this would correspond to solving the halting problem. Real-time systems however adhere to restrictions which guarantee that these programs always terminate. That is, all loops and recursions are limited and the recursion and loop bounds are known in advance.<sup>1</sup> There are two classes of methods for obtaining WCET bounds for real-time tasks:

- *Dynamic* methods derive WCET estimates from observing concrete program executions. They are also referred to as *measurement-based* methods.

- *Static* methods determine WCET bounds by applying analysis methods to the program code without executing it.

All methods make pessimistic assumptions in order to approximate the worst-case behavior. *Reliable* WCET bounds – as required for designing hard real-time systems – can only be given by methods which are safe and sound. A method is *safe* if it only uses assumptions which over-approximate the worst-case, i.e., if it errs only on the safe side. A method is also *sound* if it covers all possible executions. For WCET analysis this means covering the product of all possible inputs, program paths, and hardware states.

The following two subsections give an overview of existing dynamic and static methods for computing task-level WCET bounds. The presentation generally proceeds from the simple to the more advanced methods and tries to illustrate the historic research development without covering all of the available tools. A broad and very detailed overview of the state of the art in WCET analysis methods and tools can be found in the overview article [WEE<sup>+</sup>08].

## 2.2.1. Dynamic Methods

The simplest dynamic method for obtaining execution time information for a task is by measuring several executions of the whole task with varying inputs. The measurements can either be performed by adding instrumentation code to manipulate hardware timers, or by the use of a logic analyzer to observe certain signals (like fetching a certain instruction or writing to a special address). The drawback of this method is that the variance in the set of executions is usually large and the values are not evenly distributed. This is partly because of the range of inputs and different operating modes but also because the execution time of modern hardware, featuring caches and complex pipelines, is very sensitive with respect to the start state and execution history [HLTW03, Rei08]. There is only little chance for observing unusually small or high execution times. Even worse, virtually all observed values *underestimate* the worst-case, i.e., measurements err on the unsafe side. Because the difference between the worst-case measurement and the actual worst-case is unknown, adding

<sup>&</sup>lt;sup>1</sup>However, experience from industrial practice shows that obtaining safe and precise recursion and loop bounds often requires a fair amount of time-consuming manual analysis.

"safety" margins to account for underestimations is not safe; and even if the results overestimate the worst-case, they are often not precise enough.

Despite the inherent lack of safety, dynamic (or measurement-based) methods can be very useful for analyzing tasks with so-called *soft*, i.e., not safety-critical, WCET constraints. The main advantage over static methods is that they do not require the construction of a hardware model, which can be expensive and time consuming depending on the complexity of the modeled hardware. However, measurement-based methods require additional tracing hardware instead. Recently, built-in debugging and tracing interfaces, e.g., the Nexus interface [O'K00], have become increasingly popular for microprocessors targeting the embedded market. The Nexus interface is very convenient to use but the employed trace buffers are too small to measure the execution of a whole task. This restriction brought forth a new generation of measurement-based timing analysis tools. These tools measure the execution times of many small snippets of the task. The individual execution times are combined to a global WCET estimate, e.g, using integer linear programming [WKRP08, Sta09], or probabilistic methods [BCP02, BBN05].

Despite all efforts to combine snippet execution times safely, these tools suffer from the same lack of soundness as full-blown measurements do; it can therefore not be guaranteed that the given WCET estimates are an upper bound of the actual WCET. At the same time, it has been reported that the combination of snippet execution times often leads to high overestimations of the WCET in practice [BBK<sup>+</sup>06]. Recent efforts to take context information for the measured snippets into account [SM10] may improve on the precision issue to a limited degree.

## 2.2.2. Static Methods

A simple static approach to obtain WCET estimates on the source-code level is the use of *timing schemes* which has been proposed by Shaw [Sha89]. It works for any imperative high-level programming language and assumes that constant execution times can be assigned to atomic instructions. For straight-line code, the execution times of the atomic instructions are added up. The execution time of a conditional is given by the maximum over all cases. Loops and recursions are handled by multiplying an iteration or recursion bound with the cost of the loop or function body.

Shaw's timing schemes have several drawbacks. First, timing schemes often give very coarse WCET bounds. For example, not all iterations of a loop have the same execution time. Different iterations may execute different paths through the loop body. Hence, simply multiplying the loop bound with the worst-case iteration significantly overestimates the actual WCET in many cases. Another problem is that for tasks running on modern computer hardware it is not safe to assume that the execution time of an atomic instruction is constant. In fact, the execution time on modern microprocessors featuring caches and complex pipelines is highly sensitive with respect to the execution history [HLTW03, Rei08]. Last but not least, estimating the WCET based on high-level source code cannot give reliable results if the source

code is translated by an optimizing compiler. Such compilers apply transformations that preserve the semantics but usually decrease (or at least alter) the execution time. For example, conditionals over a variable that can be proven to be constant for any execution may be removed and loop invariant computations may be hoisted outside the loop body.

There have been attempts to overcome the limitations of Shaw's original method, applying it to assembly level programs and taking the effects of modern processor features into account. To this end, Lim et al. [RLP+94, LBJ+94] and Hur et al. [HBL+95] propose a method which models cache effects via bookkeeping of first and last references to memory blocks; pipelining effects are modeled by reservation tables whose resources are registers and pipeline stages. The approach has been evaluated for the rather simple MIPS 3000 architecture and very small programs. It is limited to such simple targets because the pipeline modeling relies on assumptions that are not valid for more advanced pipelines.

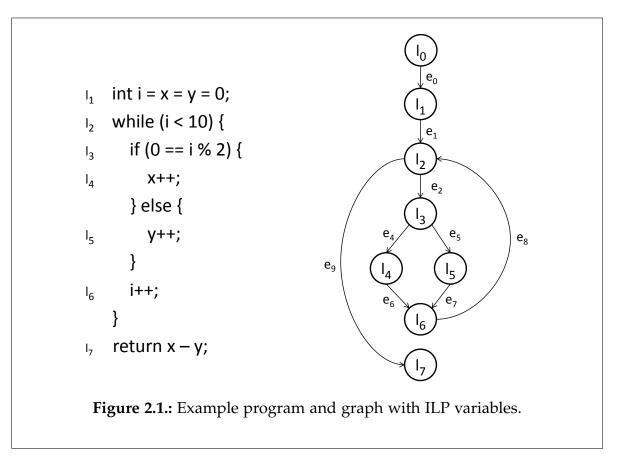

Li et al. propose the use of integer linear programming (ILP) for the static computation of WCET bounds [LMW96]. Their method captures pipelining and cache effects, as well as the task's control flow. The proposed control flow modeling has proven to be very useful for static WCET analysis, hence we discuss it in more detail. The control flow of the analyzed task is modeled as constraints of an ILP. The WCET bound of the task is computed by solving the ILP with a target function that maximizes the execution time. An example of the control flow modeling is depicted in Figure 2.1. The control flow graph on the right-hand side of the figure is decorated with variables for constructing the ILP. The variables  $l_1, \ldots, l_7$  denote the execution counts of the labeled instructions in the program and  $l_0$  is the execution count of the program entry. Similarly, the variables  $e_0, \ldots, e_9$  represent the traversal counts of the corresponding control flow edges. Based on the control flow graph of Figure 2.1, the following ILP constraints can be established:

The constraints state that the execution count of an instruction equals the sum of the traversal counts over all incoming and outgoing edges, e.g.,  $l_2 = e_1 + e_8$  and  $l_2 = e_2 + e_9$ . Furthermore, that the loop entry at  $l_2$  is executed at most ten times,  $0 \le e_2 \le 10$ , and that the whole program is executed only once,  $l_0 = 1$ . Let  $t_i$  denote the execution time for instruction  $l_i$ . The WCET bound is obtained by solving the ILP under the above constraints, maximizing the following target function, where t denotes the execution time of the whole program:

$$t = \sum_{i=1}^{7} l_i \cdot t_i$$

This technique for bounding the global execution time on the control flow graph is known as *implicit path enumeration technique* or IPET for short. It is also used in the modular, static WCET analysis framework presented in Section 5.1.

Li et al. derive the time bounds for the instructions from another ILP which models the pipeline and cache behavior. The size of this ILP depends on the complexity of the considered architecture. The published analysis times for the rather simple Intel i960KB [Cor91] processor indicate that the approach does probably not scale to more complex architectures.

Healy et al. propose a WCET analysis which uses several distinct phases [HWH95, HAM<sup>+</sup>99, AMWH94]. The first phase uses a so-called static instruction cache simulator in order to classify instruction fetches as cache hits or misses. A subsequent pipeline path analysis computes execution times for instruction sequences under consideration of the cache simulator results. The pipeline behavior is described in terms of resource usage patterns that are assigned to individual instructions. Finally, the computed execution times are combined into a WCET bound for the analyzed program. Healy et al. consider the MicroSPARC pipeline and direct-mapped caches. Again, the approach is limited to such simple microprocessors because the pipeline modeling relies on assumptions which do not hold for more complex architectures. Lundquist and Stenström obtain WCET bounds by an interpretation of the program under analysis using an abstract processor simulator [LS98, LS99b]. In contrast to

measurements or explicit simulation, the problem of covering the possible inputs is handled by allowing input ranges for the simulation. The implementation simulates the possible executions by a cycle-wise evolution of the pipeline model and performs ALU operations on ranges instead of concrete values. The WCET bound is derived from the required number of single-cycle simulator steps. Abstract simulation can give safe and tight WCET bounds if the simulation terminates. Also, the method is fully automatic. However, termination is not guaranteed and the complexity of the abstract simulation depends heavily on the number of paths that have to be followed. For example, if the outcome of a branch condition (branch taken or not taken) cannot be precisely predicted, the simulation must continue for both possibilities. The arising complexity can quickly render the analysis infeasible in practice. Lundquist and Stenström evaluate their approach using a hardware model that is based on the PowerPC architecture and rather small programs.

Engblom presents a similar approach in [Eng02]. In contrast to Lundquist and Stenström's abstract simulation, which handles everything in one monolithic analysis, it decomposes the problem into several sub-problems which are solved by separate analyses. However, at the core of the method is also an abstract simulator. The scalability problems of Lundquist and Stenström's abstract simulator are avoided by using the simulation only to compute execution times for linear sequences of instructions. The WCET estimates for all sequences are then combined into a WCET estimate for the whole program. Due to several simplifying assumptions, the approach is limited to simple architectures that are free of timing anomalies (see Section 5.3.2) and do not feature caches, e.g., the ARM7 microprocessor.

Another method for WCET analysis is proposed by Colin and Puaut [CP01]. They call their approach tree-based because it uses the syntax tree of the program under analysis to combine low-level WCET estimates to a global WCET bound. The low-level WCET estimates are obtained from independent analyses of the instruction cache and pipeline behavior. The approach has also been extended to handle dynamic branch prediction [CP00]. A weakness of the tree-based method is that it is not context-sensitive and therefore seems to produce rather pessimistic WCET estimates. Li/Mitra et al. present an analysis for an out-of-order pipeline which determines context-sensitive execution time bounds for basic blocks by a fixed point analysis of the time intervals at which instructions enter and leave the different pipeline stages [LRM04, LMR05]. The instruction cache and dynamic branch prediction behavior is analyzed by ILP-based techniques [LMR05, RLM02]. The global WCET bound is calculated using IPET. The tool only supports the processor model of the SimpleScalar [ALE02] sim-outorder cycle-accurate processor simulator.

Kirner et al. describe a WCET analysis which cooperates with a compiler and requires users to write their programs in a dedicated derivative of the C programming language with WCET annotations [KLFP02]. Execution time bounds are computed on the generated object code using ILP techniques [PS97]. Annotations are taken into account using additional compiler information, particularly in order to deal with compiler optimization [KP03]. The tool supports several simple embedded processors which are free of timing anomalies. Wilhelm et al. use an approach that decomposes the WCET problem into several sub-problems which are independently solved using a combination of abstract interpretation and integer linear programming [FHL<sup>+</sup>01, HLTW03]. The implementation starts from fully linked executables and also features analyses for predicting low-level timing effects of the hardware [Fer97, The04]. The analysis has been applied to industrial software [TSH<sup>+</sup>03, WEE<sup>+</sup>08] and the analyzer is available as a commercial product [Abs00]. Our work builds on top of this approach which is therefore discussed in detail in Section 5.1.

The research in static WCET analysis led to the development of numerous academic and commercial tools which we have not covered exhaustively, e.g., the Bound-T tool [Tid00, HLS00], or the OTAWA WCET analysis framework [BCRS10]. However, these remaining tools generally use a combination of the already mentioned techniques and deviate only in details. Again, we refer to [WEE<sup>+</sup>08] for an in-depth discussion.

## 2.3. Symbolic Methods in WCET Analysis

Symbolic methods so far have only been applied to WCET analysis in the context of symbolic model checking. Early work by Logothetis and Schneider computes WCET bounds for synchronous programs, assuming a single-cycle execution model [LS03, LSM03]. This execution model does not hold for modern processor hardware, using pipelined execution and caches to improve the average execution time. It can therefore not be directly compared with any of the already described approaches except timing schemes.

More recent research in model checking for WCET analysis by Larsen et al. also takes the timing effects of the hardware into account [DOT<sup>+</sup>10]. Pipeline, caches, and the control flow of the analyzed program are modeled as timed automata in the real-time model checker Uppaal [BLL<sup>+</sup>96, LPY97]. WCET bounds in terms of execution cycles are determined directly by a reachability analysis with the Uppaal model checker. Despite the modular modeling concept, the analysis itself is monolithic in the way that the model checker considers the combined state space of the hard- and software model. It is therefore not surprising that – according to the published results – the approach suffers from serious scalability problems even though it only addresses the most simple pipelines. The work of Larsen et al. is probably the closest to our approach. The similarities concern the modeling of the hard- and software interaction and the fact that symbolic methods are used to cover the state space of the pipeline. But there are also significant differences. Larsen et al. strive for a wholesome model checking approach whereas our work uses BDD-based symbolic methods only for covering the state space of the pipeline. Our approach is also truly modular and therefore less prone to scalability issues.

Multicore processors have recently become a major topic in the WCET research community. The interference between several tasks accessing shared resources significantly complicates the WCET problem. Currently the problem appears far from being solved and it has even been argued that generic multicore processors should not be considered for applications with WCET requirements [CFG<sup>+</sup>10]. However, the question of giving WCET bounds for multicore processors also brought forth a research paper on integrating abstract interpretation with model checking [LNYY10]. Wang et al. use an abstract cache analysis to predict the local cache behavior of each task. The interaction of the tasks on the shared bus is then modeled in Uppaal using timed automata. The problem of giving WCET bounds for multicore applications is not quite comparable to the computation of WCET bounds for single uninterrupted tasks. However, it is still interesting to compare the work of Wang et al. with our approach because it also combines abstract interpretation with symbolic state traversal. The difference is that our state traversal is not quite the same as reachability analysis by a symbolic model checker. It is tightly integrated into a static program analysis framework and allows the interaction with other analyses during analysis time (see Section 6.5 for an example).

Finally, a very different approach for using model checking in WCET analysis is taken by Wenzel et al. [WKRP08]. Their tool uses a model checker for finding feasible paths and generating the corresponding input data for measurement-based WCET estimation.

## CHAPTER 3

## Abstract Interpretation

Static program analyses answer questions about the behavior of a computer program without executing it. Their application ranges from questions about the state of variables (*what are the possible values of variable x at program point p*) to more difficult questions about correctness (*does the program never divide by zero?*). A common property of all static analyses is that they compute invariants, i.e., the given answers hold for all possible executions of the program. For any non-trivial analysis, this requires the program semantics to be taken into account. Unfortunately, all non-trivial questions about the concrete semantics of a program are undecidable. Static analyses therefore rely on *abstract semantics* which over-approximates the concrete semantics. Abstractions yield problems that are easier to compute but this is typically associated with a loss of precision. The trade-off between computability and precision makes the design of static analyses a challenging task.

A classic application of static analyses is the design of compiler optimizations. Compiler optimizations involve program transformations that must preserve the program semantics. This requires knowledge about semantic invariants which are obtained by static analyses. More recently, static analysis techniques are also employed in the verification of safety-critical systems, e.g., to prove the absence of run-time errors [BCC<sup>+</sup>03] and to compute safe upper bounds on the worst-case execution time of tasks [FHL<sup>+</sup>01].

This chapter gives an introduction into the design of abstract domains for static analyses, the actual computation of the semantic invariants, and into the underlying theory of abstract interpretation. The presentation is based on the works of Miné [Min04], Martin [Mar98, Mar99], and a text book on program analysis by Nielson, Nielson, and Hankin [NNH99].

## 3.1. Lattice Theory

The theory of *abstract interpretation* states that all kinds of semantics can be expressed as fixed points of monotonic functions in partially ordered structures. The correctness of a program analysis can be proved if the considered partially ordered structures satisfy certain conditions. This section introduces the required elements from lattice theory.

### Definition 3.1 (Partially ordered set, poset)

A partially ordered set  $(\mathcal{D}, \sqsubseteq)$  is a non-empty set  $\mathcal{D}$  with a partial order  $\sqsubseteq$ , that is a reflexive, transitive and anti-symmetric binary relation. If they exist, the greatest lower bound (glb) of a set  $D \subseteq \mathcal{D}$  will be denoted by  $\prod D$  and the least upper bound (lub) will be denoted by  $\bigsqcup D$ . The least element and greatest element of D will be denoted by  $\perp$  and  $\top$  if they exist.

#### **Definition 3.2 (Complete lattice)**

A lattice  $(\mathcal{D}, \sqsubseteq, \sqcup, \sqcap)$  is a poset where each pair of elements  $a, b \in \mathcal{D}$  has a least upper bound  $a \sqcup b$  and a greatest lower bound  $a \sqcap b$ . A lattice is said to be complete if any set  $D \subseteq \mathcal{D}$  has a least upper bound. This implies that a complete lattice has both a least element  $\bot = \bigsqcup \emptyset$  and a greatest element  $\top = \bigsqcup \mathcal{D}$ . Furthermore, each set  $D \subseteq \mathcal{D}$  has a greatest lower bound  $\sqcap D = \bigsqcup \{X \in D \mid \forall Y \in D, X \sqsubseteq Y\}$ . A complete lattice will be denoted by  $(\mathcal{D}, \sqsubseteq, \sqcup, \sqcap, \bot, \top)$ .

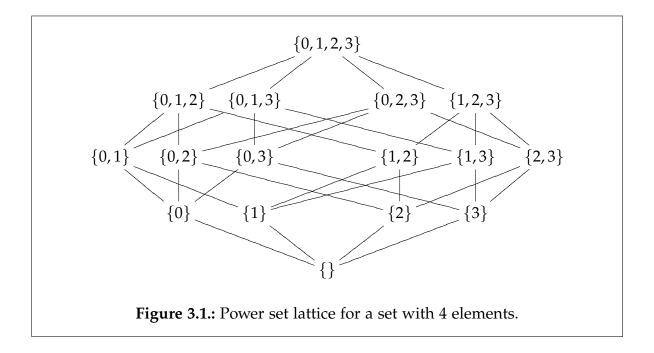

**Power Set Lattice**. An important complete lattice is the *power set lattice* which can be constructed from any set *S* using standard set operators, i.e.,  $(2^S, \subseteq, \cup, \cap, \emptyset, S)$ . An example of this lattice based on a set with 4 elements is depicted in Figure 3.1. Its height, i.e., the length of the longest path from  $\bot$  to  $\top$ , is 4. In general, a power set lattice  $(2^S, \subseteq, \cup, \cap, \emptyset, S)$  has height |S|.

**Abbreviations**. The following text will use a more compact notation for posets and complete lattices if this does not lead to ambiguities. A poset  $(\mathcal{D}^x, \sqsubseteq^x)$  will be referred to as  $\mathcal{D}^x$ , i.e., the superscript *x* will be used as an identifier for a certain poset. The same holds for lattices, i.e., the complete lattice  $\mathcal{D}^x$  is ordered by  $\sqsubseteq^x$  with lub  $\sqcup^x$ , glb  $\sqcap^x$ , least element  $\bot^x$  and greatest element  $\top^x$ .

We introduce two important properties of functions between lattices. Monotonicity is required for fixed point computation and for establishing a correctness relation between two semantic domains. The notion of distributivity of functions is related to the corresponding property of arithmetic operators.

#### **Definition 3.3 (Monotonic)**

A function  $f : D^a \to D^b$  between two posets  $D^a$  and  $D^b$  is monotonic (or order-preserving) *if*

$\forall X^a, Y^a \in \mathcal{D}^a : X^a \sqsubseteq^a Y^a \Rightarrow f(X^a) \sqsubseteq^b f(Y^a)$

#### **Definition 3.4 (Distributive)**

A function  $f : D^a \to D^b$  between two lattices  $D^a$  and  $D^b$  is distributive (sometimes called additive) if

$$\forall X^a, Y^a \in \mathcal{D}^a : f(X^a \sqcup^a Y^a) = f(X^a) \sqcup^b f(Y^a)$$

It is called completely distributive if

$$\forall D^a \subseteq \mathcal{D}^a : f(\bigsqcup^a D^a) = \bigsqcup^b \{ f(X^a) \mid X^a \in D^a \}$$

whenever  $\bigsqcup^a D^a$  exists.

#### 3.1.1. Fixed Points

A *fixed point* of a function f is an element X such that f(X) = X. If f is monotonic, the following theorem ensures the existence of fixed points.

#### Theorem 3.1 (Tarski's Fixed Point Theorem)

If  $f : \mathcal{D}^x \to \mathcal{D}^x$  is a monotonic function in a complete lattice  $\mathcal{D}^x$ , then the set of all fixed points  $Fix(f) = \{X^x | f(X^x) = X^x\}$  is nonempty and forms a complete lattice when ordered by  $\sqsubseteq^x$ .

#### Proof Found in [Tar55].

The practical computation of fixed points is based on ascending sequences of elements in complete lattices called *ascending chains*.

#### **Definition 3.5 (Ascending chain)**

An ascending chain  $(X_i)_i$  is a sequence  $X_0, X_1, \ldots$  such that  $\forall j : X_j \sqsubseteq X_{j+1}$ . It is called strictly ascending iff  $\forall j : X_j \neq X_{j+1}$ . An ascending chain is said to stabilize if it holds that  $\exists j : \forall n \ge j : X_j = X_n$ .

An example of an ascending chain in the power set lattice of Figure 3.1 is the following sequence which, in terms of the picture, ascends along the left edge of the lattice:

$\bot = \emptyset, \{0\}, \{0,1\}, \{0,1,2\}, \{0,1,2,3\} = \top$

The non-existence of strictly ascending chains naturally gives rise to an iterative computation of fixed points. This is formalized by the following theorem.

#### Theorem 3.2 (Kleene's Fixed Point Theorem)

Let  $\mathcal{D}^x$  be a complete lattice where all ascending chains eventually stabilize. If  $f : \mathcal{D}^x \to \mathcal{D}^x$  is a monotonic function, then there exists a k such that  $f^k(\perp^x) = f^{k+1}(\perp^x)$  and  $f^k(\perp^x)$  is the least fixed point of f.

Proof Found in [Cou78].

Iterative fixed point computation might not converge if the lattice has strictly ascending chains. In such cases, convergence can be enforced by the application of a *widening* operator. The obtained fixed point is typically above the least fixed point. A subsequent down iteration using a *narrowing* operator can refine such coarse overapproximation. Interval analysis is an example where widening plays an important role. It assigns an interval of natural numbers to integer variables. The top element of this lattice is the interval  $[-\infty, +\infty]$ . The analysis of a loop incrementing an integer variable *x* in every loop iteration may not reach a fixed point if it fails to determine a static bound for the number of loop iterations. Widening will force convergence by setting the interval for *x* to  $[-\infty, +\infty]$ .

Within the scope of our work, widening and narrowing are not required since we only consider lattices of finite height where convergence speed is no problem. We refer to [NNH99] for details on this subject.

## 3.2. Collecting Semantics

A static program analysis has to refer to the semantics of programs. We consider a form of semantics that is based on a program representation as a directed graph.

#### Definition 3.6 (Control flow graph)

A control flow graph (CFG) is a directed graph G = (N, E, s, e) with a finite set of nodes N, a set of edges  $E \subseteq N \times N$ , a start node s and an end node e. If there exists an edge (n,m)

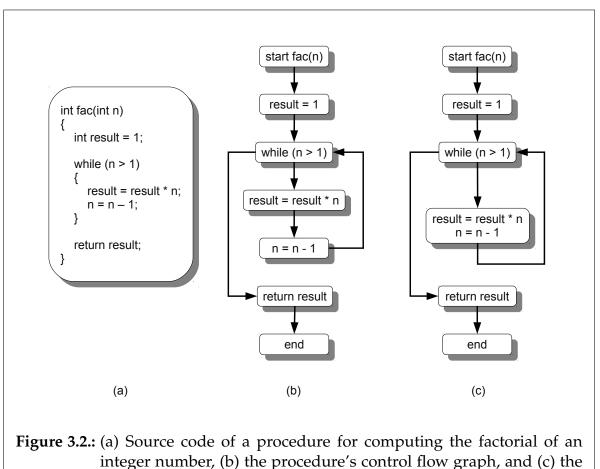

basic block graph of the same procedure.

then *n* is called predecessor of *m* and *m* is called successor of *n*. The start node *s* has no predecessor and the end node *e* has no successor.

A sequence  $(n_1, \ldots, n_k) \in N^*$  is a path through G iff  $n_1 = s$  and  $\forall j \in \{1, \ldots, k-1\}$ :  $(n_j, n_{j+1}) \in E$ . A sequence  $(n_1, \ldots, n_k) \in N^*$  is a path to n if it is a path and  $n_k = n$ . The path to the start node s is denoted by  $(s) \in N^*$ .

It is often useful to collapse maximal paths of strictly linear control flow into single blocks. This transformation yields a more compact CFG representation in which each node subsumes one or several program statements.

## Definition 3.7 (Basic block)

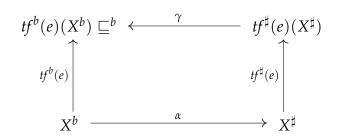

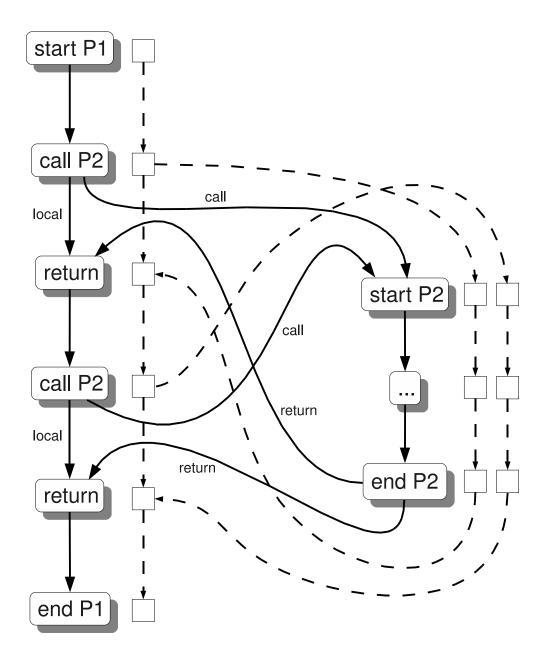

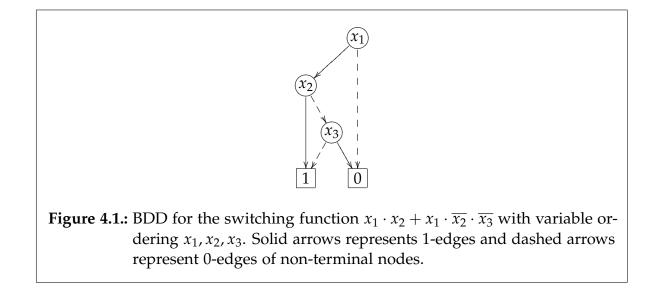

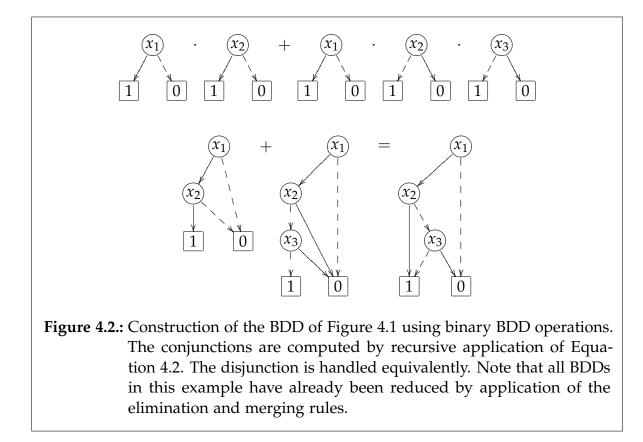

A basic block is a maximal sequence of nodes  $(n_1, ..., n_k)$  of a CFG = (N, E, s, e) such that  $n_i$  is the only predecessor of  $n_{i+1}$  and  $n_{i+1}$  is the only successor of  $n_i$  and  $n_1 \neq s$ ,  $n_k \neq e$ . A basic block graph G = (N, E, s, e) is a CFG in which every node  $n \in N$  that is not the start or end node, is a basic block.