## OS Verification Extended

On the Formal Verification of Device Drivers and the Correctness of Client/Server Software

## Dissertation

zur Erlangung des Grades des Doktors der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

Eyad Alkassar

eyad@wjpserver.cs.uni-sb.de

Saarbrücken, Juli 2009

Tag des Kolloqiums: 17.07.2009

Dekan: Prof. Dr. Joachim Weickert

Vorsitzender des Prüfungsausschusses: Prof. Dr. Kurt Mehlhorn

Berichterstatter: Prof. Dr. Wolfgang J. Paul

Berichterstatter: Prof. Dr. Gert Smolka

3. Berichterstatter: Prof. Dr. Andreas Podelski akademischer Mitarbeiter: Dr. Mark A. Hillebrand

### Danksagung

An dieser Stelle möchte ich all jenen danken, die zum Gelingen der vorliegenden Arbeit beigetragen haben.

Zunächst gilt mein Dank meiner Familie; meiner Mutter und meinem Vater, denen ich fast alles zu Verdanken habe, und meinen Geschwistern Ammar, Muhannad und Manar, auf die immer Verlass ist.

Meinem Mentor Herrn Prof. Paul danke ich ganz besonders für die Möglichkeit, meine Promotion im Rahmen eines so spannenden Projektes wie Verisoft durchführen zu können und für die wissenschaftliche Betreuung der Arbeit.

Mein Dank gilt auch meinen (ehemaligen und derzeitigen) Arbeitskollegen am Lehrstuhl von Herrn Paul. Mark (der lokales-lernen erbende-wen-wurst), Dirk (der allzeit Hilfsbereite), Norbert (der ehrenwerte Denker) und Tom (der trickreiche Menschenkenner) waren eine unschätzbare Bereicherung. Meinem Freund Steffen möchte ich ganz besonders danken für die gemeinsamen Jahre im Raum 318. Ausdrücklich danken für die gemeinsame Zeit möchte ich auch Hristo, Sebastian, Sergey, Andrey und Peter.

Schließlich bleibt mir meinem Freund Aref zu danken, dessen weiser Rat in manch schwerer Stunde unendlich wertvoll war.

This thesis work was funded by DFG Graduiertenkolleg 'Leistungsgarantien für Rechnersysteme' and by the German Federal Ministry of Education and Research (BMBF) in the framework of the Verisoft project under grant 01 IS C38.

### Abstract

This thesis tackles two important challenges in OS verification: The formal verification of device drivers and the correctness of client/server software.

Device drivers are an integral part of system software. Not only high-level functionality such as file I/O depends on devices. Even basic OS features, such as demand paging, need correctly implemented drivers. In this thesis, we show how to pervasively integrate devices and their drivers into a language stack reaching from the level of assembly up to high-level languages. This stack is leveraged for the formal verification of a simple hard disk driver, which is subsequently embedded into Verisoft's micro kernel. To the best of our knowledge, this marks the first formal functional verification of a device driver against a realistic device and system model.

Remote procedure calls (RPCs) lie at the heart of any client/server software. In the second part of this thesis, we present a specification of an RPC mechanism and we outline how to verify an implementation of this mechanism at the code level. The formalization is based on a model of user processes running concurrently under a simple OS, which provides inter-process communication and portmapper system calls. A simple theory of non interference permits us to use conventional sequential program analysis between system calls. To the best of our knowledge this is the first treatment of the correctness of an entire RPC mechanism at the code level.

### Zusammenfassung

Diese Arbeit behandelt zwei wichtige Probleme in der Verifikation von Betriebssystemen (BS): Die formale Verifikation von Gerätetreibern und die Korrektheit von Client/Server Software.

Grundlegende Funktionen eines BS, wie z.B. Demand Paging, setzen korrekt implementierte Treiber voraus. In dieser Arbeit zeigen wir auf, wie Geräte nahtlos in allen Semantikschichten integriert werden können — von Assembler bis hin zu einer C ähnlichen Hochsprache. Diese durchgängige Theorie wird anschließend verwendet, um einen einfachen Festplattentreiber (Teil des Verisoft Mikrokerns) formal zu verifizieren. So weit uns bekannt, stellt dies die erste formale Verifikation eines Treibers im Kontext eines realistischen Geräte- und Systemmodells dar.

Implementierungen von Client/Server Software basieren oftmals auf Remote Procedure Calls (RPCs). Im zweiten Teil dieser Arbeit, spezifizieren wir einen solchen RPC Mechanismus und skizzieren dessen Verifikation auf Codeebene. Die Formalisierung basiert auf einem Modell von Benutzerprozessen die nebenläufig in einem einfachen BS ausgeführt werden. Dieses BS stellt Interprozess-Kommunikation und Portmapper Funktionalität über spezielle Systemaufrufe zur Verfügung. Um sequentiell über einzelne Prozesse argumentieren zu können, führen wir eine kleine Theorie zur Bestimmung der Abhängigkeit von Systemaufrufen ein. So weit uns bekannt, behandelt diese Arbeit erstmals die Korrektheit eines vollständigen RPC Mechanismus auf Codeebene.

# Contents

| 1  | Inti | roduction                                         | 3   |

|----|------|---------------------------------------------------|-----|

|    | 1.1  | Structure of the Document                         | 7   |

|    | 1.2  | Related Work                                      | 7   |

|    | 1.3  | The Setting                                       | 10  |

|    | 1.4  | Notation                                          | 13  |

| 2  | Roa  | ad Map                                            | 17  |

|    | 2.1  | Formal Verification of Device Drivers             | 17  |

|    | 2.2  | Verification of Client/Server Software            | 19  |

| Ι  | Fo   | rmal Function Verification of Device Drivers      | 21  |

| 3  | Ext  | ending the Language Stack                         | 23  |

|    | 3.1  | VAMP and Devices                                  | 23  |

|    | 3.2  | VAMP Reordered                                    | 45  |

|    | 3.3  | C0 and Devices                                    | 52  |

|    | 3.4  | C0 With Inline Assembly                           |     |

|    | 3.5  | C0 With XCalls                                    | 83  |

| 4  | Cas  | e Study: Hard Disk Driver                         | 97  |

|    | 4.1  | Hard Disk Model                                   | 98  |

|    | 4.2  | Assembly Driver                                   | 107 |

|    | 4.3  | C0 Driver                                         | 119 |

| II | Pr   | oving the Correctness of Client / Server Software | 133 |

| 5  | Spe  | cifying an Operating System                       | 135 |

|    | 5.1  | Background                                        |     |

|    | 5.2  | Specification of the SOS                          |     |

|    | 5.3  | Reasoning About Applications in SOS*              | 152 |

| 6  | Pro  | wing Correctness of Client/Server software        | 159 |

2 CONTENTS

|    | 6.1   | The Programming Language C0                   | 160 |

|----|-------|-----------------------------------------------|-----|

|    | 6.2   | Signatures of Services                        | 161 |

|    | 6.3   | Portmapper Correctness                        | 162 |

|    | 6.4   | Sending and Receiving Data Structures         | 163 |

|    | 6.5   | RPC Client Protocol                           | 168 |

|    | 6.6   | Building a Server and Proving its Correctness | 172 |

| 7  | Con   | clusion and Future Work                       | 177 |

|    | 7.1   | Formal Work                                   | 178 |

|    | 7.2   | Future Work                                   | 179 |

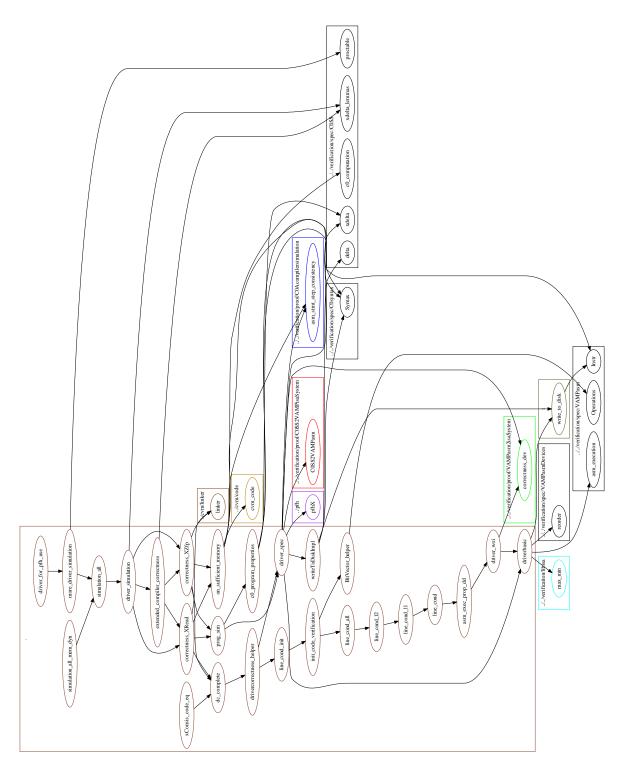

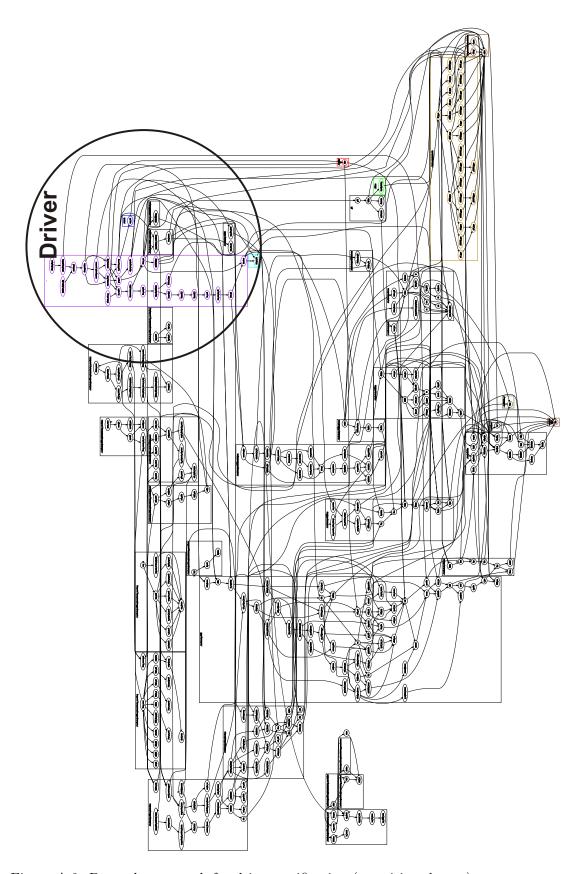

| A  | Dep   | endency Graphs                                | 181 |

| В  | Map   | oping to Formal Names                         | 185 |

| Bi | bliog | graphy                                        | 187 |

## Chapter 1

## Introduction

The heart beat of our society If technology is labeled the new religion of our modern society, software developers should be called its high priests. In almost all niches of our daily life we are at their mercy, believing in the infallibility of their products: When we drive to work with the car, dozens of programs—from the entertainment system to the airbag control—assist us and ensure that we reach our destination safely. When we travel around the world with the airplane, most of the time a program is flying. Future presidents and rulers are elected at black boxes, in which a program counts the vote. And finally, when we get old, even the beat of our heart is controlled by a piece of software running in the pacemaker.

Even though a single error in a single code line may destroy hundreds of lives, society responds surprisingly calm. From where comes this unbounded trust? There are four ways to deal with the threat of software errors.

Followers of the first way—lets call them traditionalists—claim that it worked out in the past, so why shall we bother about the future? This argument has three major flaws. Firstly, it is impudent to plead on the record of a technology which did not exist two generations ago. Since then, the tremendous increase of the application domain of computer systems has been probably singular in the history of technology. Secondly, it did not work out so far; there is already an alarming record of catastrophes caused by bugs in programs. Here, only one example for illustration: The death of at least five people could be directly ascribed to a bug in the code controlling the Therac-25 radiation therapy machine when it administered excessive quantities of Xrays [Lev93]. In 2002 a study of the US National Institute of Standards and Technology came to the result that 'software bugs, or errors, are so prevalent and so detrimental that they cost the U.S. economy an estimated \$59.5 billion annually, or about 0.6 percent of the gross domestic product'. And, thirdly, even if we ignore these facts, a single worst-case scenario, say an error in the cooling system of a nuclear power plant, may be too expensive for us to afford.

Much more rational is the physicist approach. Physicists, first build mod-

els, called theories, of the world. They measure the plausibility of these theories by the degree of falsifiability, i.e. by exposing them to experiments, testing them for flaws against the real world. This is quite similar to the state of the art in industrial software quality management, which is extensive testing. The real world corresponds to the implementation of the running computer system, the theories are called formal specifications, and test-vectors are merely more than experiments. Even though this approach is much more justified to be trusted than the traditionalist one, on the long run it is futile. With a complexity of programs increasing in an exponential way, it is almost impossible to ensure that no bugs are left undetected. Take for example operating systems: within twenty years the program size increased by several orders of magnitude, from a few hundred kilobytes (MS DOS) to over a Gigabyte (Windows 7). As physicists never claim the correctness of their theories, testing cannot prove the absence of errors, either.

*Proofs*, yet, lie in the domain of mathematicians. They not only claim correctness of theorems. But they have developed precise rules, called axioms, to formalize and to derive the validity of such claims. Correspondingly, one could axiomatize software systems and deduce correctness properties. Still, the mathematicians' approach suffers from a serious problem: Who ensures that the proof has been correctly deduced? What is the worth of a 'proof' written down on hundred of pages, whose formalism is only understood by a handful experts? The answer is probably: not much, as the following example illustrates. An important result in topology, the jordan curve theorem, was found by Camille Jordan. He stated in his publications in 1887 'that this theorem is clearly true' and provided a proof which later on was dismissed over decades as insufficient or simply as wrong. In 1905 Oswald Veblen claimed a new proof, which however used a series of 'intuitive' arguments making it hard do determine its truth value. The solution was reached in 2005 when a computer checked proof was conducted by Hales [Hal07] (he also found out that Jordan's original proof did not contain any serious flaw).

This, finally, may be also the silver bullet for trusting computer systems: formal verification. Formal verification, the computer scientists' approach, comprises components of all three mentioned ways: implementations of computer systems are axiomatized and verified against formal specifications. These proofs are then computer checked, giving us the ultimate amount of confidence. Nevertheless, the specification still has either to be tested or simply to be trusted.

**Pervasive System Verification as a Scientific Task** This approach was pioneered by, among others, Dijkstra, Flyod, Lamport, and Hoare. Up to now most approaches in formal verification only model some limited parts or high-level layers of an overall system. Underlying layers are either modeled in some semi-formal way or some *perfect* (i.e. correct) and simplified model is even

postulated, claiming an accurate model would be too complex to build. For example when a concrete application, as a fingerprint authentication software, running on top of a real operating system, as *Linux*, should be verified, it is not enough only to prove the correctness of the abstract fingerprint matching algorithm. This is because the specification of this algorithm may use some model of the services provided by the operating system, assuming both correctness of modeling and of functionality of the services. Moreover, only very few approaches carry out the verification at the level of *concrete code*.

Now, would the goal to pervasively formalize and verify the correctness of a computer system, from transistors to software not be a major scientific task? Having in mind that proving comes closest to understanding, would it not be worthwhile to entirely understand one of the probably most complex creations of men? In [Moo03] J. S. Moore, principal researcher of the CLI stack project [BHMY89], gives a strongly affirmative answer to this question and declares the formal verification of a 'practical computing system' as a grand challenge problem.

A main goal of the Verisoft project [The09] is to tackle this challenge. In the academic system, a subproject of the Verisoft project, a general-purpose computer system, covering all layers from the gate-level hardware description to communicating concurrent programs should be designed, implemented and verified. The verification is supposed to be pervasive throughout all layers of abstraction and all models and proofs should be formalized and checked in a single mechanized language, Isabelle/HOL [NPW02].

Motivation for the thesis Almost a decade prior to the Verisoft project the well-perceived CLI stack project [BHMY89] tackled the challenge of pervasive system verification — but left many issues open. Even though, impressive progress had been accomplished, several crucial issues have not been treated. Among those, most prominently, the integration and verification of device drivers and of high level applications, as client/server software, were omitted. This thesis tackles these two open challenges within Verisoft:

• Formal device driver verification. Device drivers are an integral part of system software. Not only high-level functionality such as file I/O or networking depend on devices. Even basic operating system features, such as demand paging, need correctly implemented drivers. Hence, any verification approach of computer system stacks should deal with driver correctness. Nevertheless, when proving functional driver correctness it does not suffice to reason only about code running on a processor. Devices themselves and their interaction with the processor also have to be formalized. On the lower-level this results in a computational model, in which the devices and the processor take turns in execution. Even in this concurrent context, the verification can be kept largely sequential and modular with respect to the other devices. This is made possible

by sound reordering of computation traces, given that devices do not interfere with each other and the driver monopolizes a single device.

In this thesis, we show how to pervasively and formally integrate devices and their drivers into a language stack reaching from the level of assembly up to the level of high-level languages. This stack is leveraged for the formal verification of a simple hard disk driver, which is subsequently embedded into the correctness of the micro kernel used in Verisoft. To the best of our knowledge, this marks the first formal functional verification of a device driver against a realistic device and system model. The extension of the language stack, the verification of the hard disk driver (write function) and its embedding into kernel correctness have been accomplished formally in the computer-aided verification system Isabelle/HOL.

The results reported in this context are based on the following publications. The overall verification approach in the Verisoft project is described in [AHL<sup>+</sup>08]. The extension of the language stack to reason about devices can be found in [AHL<sup>+</sup>09, AHL<sup>+</sup>08]. The assembly verification of the hard disk driver and a small reordering theory for the concurrent system was published in [AH08]. In [ASS08] we report on its integration in the kernel. The specification of other device models, as the serial interface can be found in [AHK<sup>+</sup>07].

• Proving the Correctness of Client Server Software. For a long time programmers struggled with the time consuming implementation of communication protocols for distributed systems. In 1984 Birell and Nelson [BN84] responded to this problem and proposed the first Remote Procedure Call (RPC) mechanism. They suggested to allow programs to call procedures located on other machines. When a process on machine A (client) calls a procedure on machine B (server), the calling process on A is suspended, and execution of the called procedure takes place on B. The caller eventually regains control, extracts the results of the procedure, and continues execution. Information can be transported from the caller to the callee in the parameters and return in the procedure result. Neither message passing nor I/O is visible to the programmer. RPC became a widely-used technique that underlies many distributed operating systems [TR85].

Thus, lying at the heart of any client server software, the formal specification and verification of RPC mechanisms is a prerequisite for the verification of any such software. In this thesis, we present a mathematical specification of an RPC mechanism based on the formalization of the Simple Operating System (SOS) [Bog08]. Furthermore, we outline how to prove the correctness of an implementation of this mechanism at

the code level. To the best of our knowledge this is the first treatment of the correctness of an entire RPC mechanism at the code level.

The results on client/server correctness have been published in [ABP09].

The most challenging aspect of this work is to pervasively integrate a wide range of models, theories, and proofs—work of many researchers at different locations—to finally obtain correctness theorems which target the whole computer stack. This has been accomplished formally in Isabelle/HOL for the device driver part and on paper for client/server correctness. Major parts of the formal theories of Verisoft have been published or are in the process of publication [HP08].

### 1.1 Structure of the Document

The thesis is structured as follows. In the remainder of this chapter we first give an overview on the related work; then we sketch the system and language stack developed in Verisoft and point out our contribution therein; and finally we summarize the mathematical notation used in this work. Chapter 2 is designed as an road map for the theories and theorems given in the thesis. Part I of the thesis deals with functional formal driver verification:

- In Chapter 3, we develop methodology and extend the current Verisoft stack to embed reasoning about device drivers.

- In Chapter 4, this stack is leveraged to verify a simple hard disk driver and integrate it into overall kernel verification.

Part II of the thesis shows how correctness of client/server software is proven.

- In Chapter 5, the underlying formal model of the simple operation system is introduced.

- In Chapter 6, upon this model we specify an RPC mechanism and prove the correctness of a simple math server.

Finally, in Chapter 7 we outline possible future work and conclude.

### 1.2 Related Work

In the following, we discuss related work within each of the four areas, which are: system software verification, reordering theory, device modeling and driver verification, as well as RPC.

System stack verification First attempts to use theorem provers to specify and even prove correct operating systems were made as early as the seventies in PSOS [NF03] and UCLA Secure Unix [WKP80]. However a missing or to a large extend underdeveloped tool environment made mechanized verification futile. With the CLI stack [BHMY89], a new pioneering approach for pervasive system verification was undertaken. Most notably the simple kernel KIT was developed and its machine code implementation was proven correct. Compared to modern kernels KIT was very limited, in particular it lacked the interaction with devices. The project L4.verified [HEK+07a] focuses on the verification of an efficient microkernel, rather than on formal pervasiveness, as no compiler correctness or an accurate device interaction is considered. The microkernel is implemented in a substantial subset of C, including pointer arithmetic and an explicit low-level memory model [TKN07]. However with inline assembly code we gain in Verisoft an even more expressive semantics as machine registers become visible if necessary. So far only exemplary portions of kernel code were reported to be verified, the virtual memory subsystem uses no demand paging [TK04]. For code verification the L4. verified project relies on Verisoft's Hoare logic environment [Sch06].

In the FLINT project, an assembly code verification framework is developed and code for context switching on a x86 architecture is formally proven correct [NYS07]. Although a verification logic for assembler code is presented, no integration of results into high-level programming languages has been reported yet. The VFiasco project [HTS02] aims at the verification of the microkernel Fiasco implemented in a subset of C++. Code verification is performed in an embedding of C++ in PVS and there is no attempt to map the results down to the machine level.

Moreover, we refer the interested reader to [Kle09], in which Klein provides an excellent and comprehensive overview of the history and current state of the art in operating systems verification.

**Reordering theory** Reordering is used in this thesis in two different flavors: for reasoning about the concurrent execution of a processor and devices, and for determining non-interference properties on operating system calls.

The reordering of execution sequences to obtain atomic specifications was studied in literature under the topic of reduction theorems. Lipton proved safety properties of pre-/ post-condition style sequentially and propagated these to the implementation [Lip75]. Cohen and Lamport extended this to liveness and a more fine-grained analysis of the reordered parts of the sequence [CL98, Coh00]. Most reduction theorems assume that the implementation fulfills some non interference theorems. In contrast we prove this assumption on the atomic specification by exploiting a similar insight as reported in [SC06]. Justified by the memory mapped I/O architecture and the SOS semantics respectively, the theories presented here are a specialization, enabling us to

formulate even stronger reduction theorems than reported in the literature.

Drivers So far most device related verifications have either targeted the correctness of gate-level implementations or safety properties of drivers. In approaches of the former kind, simulation and test based techniques are used to check for errors in the hardware designs. In particular, [BKS03, RPS01] deal with serial interfaces in that manner. In approaches of the latter kind the driver code is usually shown to guarantee certain API constraints of the operating system and hence cannot cause system crashes. For example, the SLAM project [BR01] provides tools for the validation of safety properties of drivers written in C. SLAM's success led to the deployment of the Static Driver Verifier (SDV) as part of the Windows Driver Foundation [Mic04]. SDV automatically checks 65 safety rules concerning the Windows Driver API for device drivers. Hallgren et al. [HJLT05] modeled device interfaces for a simple operating system written in Haskell. Three memory-mapped I/O calls were specified: read, write, and test for valid region. However, the only correctness property being stated is the disjointness of the device address spaces.

In contrast to all mentioned approaches, we aim at the formalization and functional verification of drivers interacting with a device. Thus, it is not sufficient to argue about the device or programming model alone. Even in other ongoing systems verification projects, the L4.verified project [HEK<sup>+</sup>07b] and the FLINT project [FLI], device behavior and driver correctness are not considered. To our knowledge, the only work similar in scope is the challenge proposed by Holzmann [Hol06] dealing with the formal verification of a file system for a Flash device. In response to the challenge, Woodcock reports on the partial specification of the file system (the 'file store') and a refinement proof mapping the store to a Java program [FFW07]. Simultaneously, the Flash hardware is being formalized [BW07]. Verifying a low-level Flash driver and integrating it into the filesystem proofs are future work. Concurrency is not an issue since only a single device is considered.

Two earlier Verisoft publications are relevant for our work. In [HIP05] paper-and-pencil models and proofs related to a simple disk driver are reported. We extend this work in three important ways: models and proofs are formalized in Isabelle/HOL, and the models are now concurrent instead of lock-step. Thus, they are not restricted to disks, which are 'simple' for lack of external communication. Moreover, in this thesis we formally integrate the proofs into the higher language stack. In [AHK+07] we have reported on formal models of a serial interface and an architecture with devices, but not treated drivers.

**Client/Server** A well-known implementation of RPC was provided by Sun Microsystems [Sri95]. The best example for an application using RPC is probably the network file system (NFS) [SCR<sup>+</sup>03].

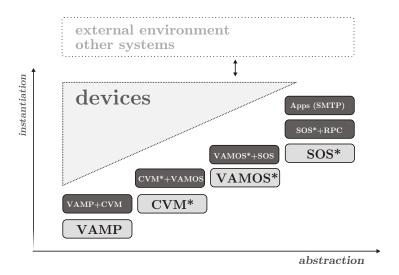

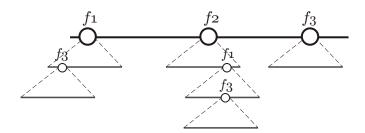

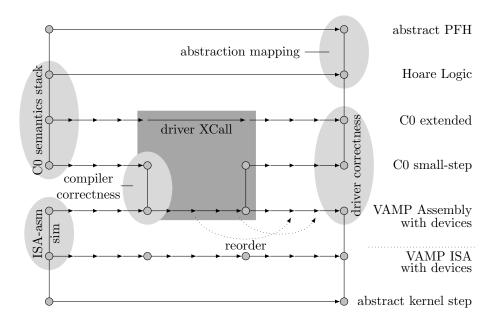

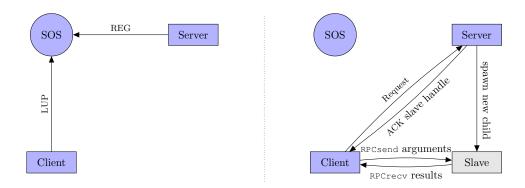

Figure 1.1: Verification stairs of the academic system (Verisoft) — Abstract models with star, implementation models without

The challenge of verifying a simple RPC memory system proposed 1994 by Broy and Lamport triggered a widespread response. The result was impressive: as many as 15 different solutions were published [BMS96]. Their goal, however, was to compare different formalization techniques and proof methods on an abstract case-study for distributed computing—rather than providing programmers with a verified RPC mechanism. In contrast, we are aiming at demonstrating that verification of RPC in a real setting, running under a real operating system is feasible. Our specifications have been used to specify and partially prove properties of user applications [LNRS07, BBBW07].

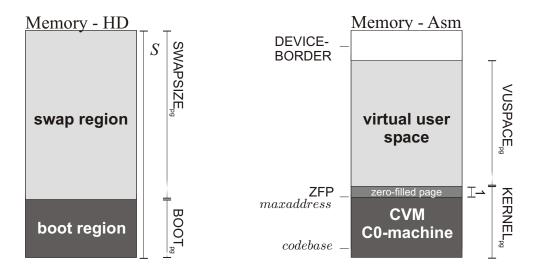

## 1.3 The Setting

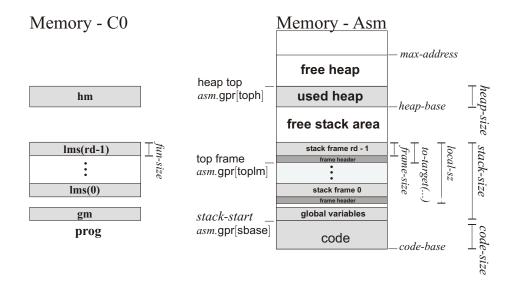

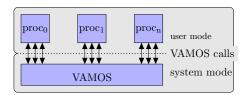

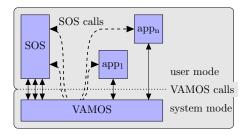

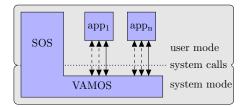

System Stack. Our system stack comprises many layers. A model of one layer is derived from the model of the (next) lower layer by means of instantiation and abstraction (cf. Figure 1.1). The hardware architecture is called VAMP [Tve09], a DLX like processor that supports address translation and memory-mapped I/O devices. With the next level of communicating virtual machines (CVM) a hardware-independent programming interface for a microkernel is provided [IT08, Tsy09]. This establishes the notion of separate concurrent user processes with virtual memories. Memory virtualization is implemented by means of demand paging [Sta09], which in turn relies for page swapping on the invocation of a hard disk driver. Parts of the CVM (as the hard disk driver) are implemented in assembly, because C0, our main im-

Figure 1.2: Semantics stack

plementation language and a subset of C, lacks some low-level programming constructs. On the basis of the CVM our *microkernel* VAMOS [DDB08] is programmed in pure C0 (with external functions provided by the CVM). The *simple operating system* (SOS) is implemented as a (privileged) user process of VAMOS [Bog08]. It offers file I/O, network access and inter-process communication. On top of it user applications are provided with a client/server architecture based on remote procedure calls [ABP09]. Finally these user applications implement the functionality of the academic system: signing software, SMTP client and server [LNRS07], and a simple email user agent [BHW06]. The implementation stack is also depicted in Figure 1.1.

The contribution of this thesis to the system stack is twofold. First, we formally verify and embed the correctness of a hard disk driver into the overall verification of the CVM. Moreover, in the course of the formal integration, we met a series of unforeseen difficulties, as for example the necessity to reason about memory consumptions of compiled code. We solve this problems, by developing and verifying general methodology. Second, on top of the SOS we deliver a new model, which supports RPC primitives and allows to implement and verify client/server applications.

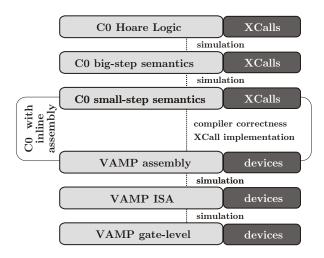

Next, we introduce the semantics stack which is orthogonal to the system stack described before. With the semantics stack a convenient Hoare logic to reason about the sequential parts of C0 programs (without inline assembly code) is established. We extend this stack to provide means to deal in Hoare logic with assembly code and to integrate devices.

Semantics Stack. The C0 semantics stack comprises a Hoare logic, a bigstep semantics, and a small-step semantics, and can be continued to the VAMP machine level, which is divided further into assembly layer, instruction set architecture, and gate-level hardware. An overview is depicted in Figure 1.2. By a higher level of abstraction in the Hoare logic compared to the small-step semantics, efficiency for the verification of individual C0 programs is gained. However, since the semantics stack is merely a proof tool for C0 programs, the results obtained in the Hoare logic have to integrate into our systems stack. The stack supplies soundness and simulation theorems that permit the transfer of program properties from the Hoare logic down to the small-step semantics. Those properties can be mapped to assembly machines by applying compiler correctness. We can get further down to the ISA layer by employing a simulation theorem and finally to the hardware by employing a processor correctness result.

The Hoare logic provides sufficient means to reason about pre and post-conditions of sequential, type-safe, and assembly-free C0 programs. Compiler correctness, though, is formulated at the small-step semantics level. This allows the integration with inline assembly code or concurrent computations, e.g. introduced by devices. The big-step semantics is a bridging layer, which is convenient to express the results of the Hoare logic operationally. The differences reflect the purpose of the layers. The Hoare logic is tuned to support verification of individual programs, whereas the small-step semantics is nearer to the architecture level.

Up to now we have argued how to bring the results down to the lower levels such that we can conduct reasoning at a comfortable abstraction level. However, this comes at the cost of expressiveness, as the lower levels not only introduce 'unnecessary clutter'. Most prominently, the levels below C0 allow the integration of devices, which are a concurrent source of computation. As soon as we attempt to reason about C0 programs that use these devices we either have to be able to express device operations at the Hoare logic level or we are doomed to carry out the whole verification at the assembly level. Our approach is to abstract the effect of those low-level computations into atomic XCalls (extended calls) in all our semantic layers. The state space of C0 is augmented with an additional component that represents the state of the external component, e.g. the device. An XCall is a procedure call that makes a transition on this external state and communicates with C0 via parameter passing and return values. With this model it is straightforward to integrate XCalls into the semantics and into Hoare logic reasoning. The XCall is typically implemented in assembly. An implementation proof of this piece of assembly justifies the abstraction to an atomic XCall.

Somewhat similar to the XCalls in the C0 semantics layers [Sch06], devices are added to all the semantic layers of the VAMP. Their state and transition functions are shared between all layers. These transition functions as well as the VAMP semantics describe small-step computations, which are interleaved

1.4. NOTATION 13

to obtain the concurrent computation of the combined system. One central prerequisite to employ our individual transfer and correctness results to obtain a global property for the combined system is to disentangle the different computations by means of reordering.

This thesis contributes to the semantics stack by integrating devices at the assembly level and by introducing the concept of XCalls to reason about low-level entities in higher level languages. By this we develop a pervasive methodology to formally verify functional correctness of device drivers and reason about them in Hoare logic. This is in particular challenging, since it integrates the concurrent computations of the processor and devices at the architecture level into the sequential view provided by the C0 (and assembly) language.

### 1.4 Notation

Basic types, terms and operations The basic sets used in this document are  $\mathbb{N}$  (naturals including zero),  $\mathbb{Z}$  (integers),  $bool = \{\text{true}, \text{false}\}$  (booleans),  $\mathbb{B}$  (binary digits) and string (strings). The sets  $type_n$ ,  $fun_n$ ,  $var_n$ ,  $field_n$  denote names and are all assumed to be subsets of string. The power set of A is denoted by pow(A).

For the numeric types we take the operations: - (subtraction), + (addition),  $\div$  (integer division),  $\cdot$  (multiplication), mod (modulo), and  $\sum$  (sum) for granted. With a dvd b we express that b is dividable by a. For an operation op  $\in \{+,-,\cdot\}$  we additionally define corresponding operations modulo 32 as follows: a op<sub>32</sub> b = (a op b) mod  $2^{32}$ .

For boolean expressions we assume that the basic logical operations:  $\land$  (conjunction),  $\lor$  (disjunction), and  $\lnot$  (negation) are defined. We write  $\exists$  for the existential quantifier and  $\forall$  for the universal quantifier. The type of a quantified variable is omitted, if it can be inferred otherwise. Moreover, we may write  $p(\dots)$  instead of  $\forall x \,.\, p(x)$ , and p(?) instead of  $\exists x \,.\, p(x)$ . An implication is denoted by  $\Longrightarrow$  and equivalence by  $\equiv$ . Moreover, we use inference rules of the form  $\frac{a}{c}$  to denote implications  $a \land b \Longrightarrow c$ .

For terms, besides the ordinary **if** -**then** -**else** expression we use abbreviations. We write **let**  $x_0 = y_0; ...; x_n = y_n$  **in**  $e(x_0, ..., x_n)$  as an abbreviation for  $e(y_0, ..., y_n)$ . Note that an assignment in a **let** expression may be nontrivial. This is because pattern matching can be used. We write, for example, **let**  $(x_0, x_1) = (y_0, y_1)$  **in**  $x_0 + x_1$  to simultaneously assign abbreviations for  $x_0$  and  $x_1$ , which are later used separately.

**Binary Operations** The set of bitstrings of length n is denoted by  $\mathbb{B}^n$ . Given a bitstring  $a = a_0 \dots a_n$ , we denote with  $a_i$  the *i*th bit of the string. The common bitwise logic operations  $\wedge_n$  (bitwise and),  $\vee_n$  (bitwise or),  $\otimes_n$

(bitwise exclusive or) and shift operations  $<<_n^l$  (logical left shift),  $>>_n^l$  (logical right shift) and  $>>_n^a$  (arithmetic left shift) are taken for granted.

We interpret bitstrings either as (unsigned) binary or (signed) two's complement numbers. The bitstring a denotes the binary number  $\langle a \rangle_n = \sum_{i=0}^{n-1} a_i \cdot 2^i$  and the two's complement number  $[a]_n = -2^{n-1} \cdot a_{n-1} + \sum_{i=0}^{n-2} a_i \cdot 2^i$ . With bitstrings of length n one could encode binary numbers in the set  $\{0,\ldots,2^n-1\}$  and two's complement numbers in the set  $\{-2^{n-1},\ldots,2^{n-1}-1\}$ . On the counterpart the functions to-bin and to-two denote the translations from numbers to bitstrings.

We expand operations on bitstrings to integers as follows. Given the two integers a and b, then the operations  $\operatorname{\sf op}^t$  with  $\operatorname{\sf op} \in \{\vee_n, \otimes_n, <<_n^l, >>_n^l, >>_n^a, +_n, -_n\}$  are defined by  $a \operatorname{\sf op}^t b \equiv [(to\text{-}two(a) \operatorname{\sf op}\ to\text{-}two(b))]_n \mod 2^n$ .

Functions and sequences We use common lambda notation to define functions, for example for addition we may write  $\lambda x \, y \, . \, x + y$ . Functions are always assumed to be total. Any function may, however, return with the special value undef, denoting that the function is undefined at this position. We denote with the range of a function f all possible outputs, i.e  $range(f) \equiv \{y|y \neq undef \land (\exists x. f(x) = y)\}$ . Analogously, the domain of a function is defined by  $dom(f) \equiv \{x|f(x) \neq undef\}$ . Updates to a function f at position g to value g are abbreviated by g and g are g are g and g and g are g and g a

Functions with domain  $\mathbb{N}$  are called sequences. We say a predicate Q is live in some sequence seq if Q is infinitely often true:  $live(seq,Q) = \forall i . \exists j > i . Q(seq(j))$ . Next, we introduce filters on sequences. A filter is a function which takes a sequence and a predicate as input. It returns a new sequence in which all elements are filtered out for which the predicate does not hold. We first define the function next which returns for a given sequence seq, predicate Q and position number k, the smallest position number l > k in the sequence seq at which Q holds.

$$next(seq, Q, k) = \begin{cases} l & \text{if } l > k \land Q(seq(l)) \land (\forall i < l.i > k \implies \neg Q(seq(i))) \\ undef & \textbf{otherwise} \end{cases}$$

We define the filter now, by the following helper function  $filter_h$ :

$$\begin{array}{lcl} \mathit{filter}_h & (\mathit{seq}, Q, 0) & = & \mathbf{if} \ \mathit{Q}(\mathit{seq}(0)) \, \mathbf{then} \, 0 \, \mathbf{else} \, \mathit{next}(\mathit{seq}, Q, 0) \\ & (\mathit{filter}_h, Q, n+1) & = & \mathit{next}(\mathit{seq}, Q, \mathit{filter}_h(\mathit{seq}, Q, n)) \end{array}$$

$$filter(seq, Q) = \lambda n.seq(filter_h(seq, Q, n))$$

Obviously, applications of the filter function are not always well-defined. This holds for example if the given predicate is never fulfilled. The following lemma shows that liveness is a criteria for well-defined filters:

1.4. NOTATION 15

### Lemma 1 (Well-defined filters)

$$live(seq, Q) \implies \forall i.next(seq, Q, i) \neq undef$$

**Tuples** Let  $T_1, ..., T_n$  be types. Then the tuple type  $T_1 \times ... \times T_n$  yields the set of all elements  $(v_1, ..., v_n)$  with  $v_1 \in T_1, ..., v_n \in T_n$ . Tuples of size two (i.e. for n = 2) are called pairs. Given a pair (a,b), then we define the two access operators first and second as follows: fst((a,b)) = a and snd((a,b)) = b.

**Records** Let  $T_1, ..., T_n$  be types,  $\mathsf{fn}_1, ..., \mathsf{fn}_n$  be strings. Then the record type  $(\mathsf{fn}_1: T_1, ..., \mathsf{fn}_n: T_n)$  yields the set of all elements  $(\mathsf{fn}_1 = v_1, ..., \mathsf{fn}_n = v_n)$  with  $v_1 \in T_1, ..., v_n \in T_n$ . Let r be a record of type  $R = (\mathsf{fn}_1: T_1, ..., \mathsf{fn}_n: T_n)$ . We denote the access to the record field  $\mathsf{fn}_i$  with  $r.\mathsf{fn}_i$ . An Update to the field  $\mathsf{fn}_i$  by a value v is abbreviated by  $r[\mathsf{fn}_i:=v]$ . It yields the new record  $(\mathsf{fn}_1 = r.\mathsf{fn}_1, ..., \mathsf{fn}_i = v, ..., \mathsf{fn}_n = r.\mathsf{fn}_n)$  if  $i \in \{0, ..., n\}$  and is undefined otherwise.

**Abstract data types** Let  $T_{1.1}, ..., T_{1.m_1}, ..., T_{n.1}, ..., T_{n.m_n}$  be types and  $C_1, ..., C_n$  be constructor names. We declare an abstract datatype T as:

If, for example  $(x_{1.1}, \ldots, x_{1.m_1}) \in T_{1.1} \times \ldots \times T_{1.m_1}$  then  $C_1(x_{1.1}, \ldots, x_{1.m_1})$  is an element of the above defined abstract data type. Note, that abstract data types may be defined recursively. Pattern matching may be used on the abstract data type either in function definitions, or by the **case-of** construct.

Sometimes we use parametrized types, which are functions taking a type and constructing a new one. Usually we denote such type functions by  $\alpha$  T, where  $\alpha$  is the type parameter.

An example of a parametrized abstract data type is the option type. It has two constructors, NONE and SOME:

For convenience we abbreviate NONE with  $\bot$  and SOME(x) with  $\lfloor x \rfloor$ . We define the selection operator the by the $(\lfloor x \rfloor) = x$  and the $(\bot) = undef$ . Option types are often used to specify the output of computations. Then,  $\bot$  stands for a computation that is stuck.

**Lists** We define a list type over elements of type  $\alpha$  as a recursive data type, with two constructors, one for the empty list and one for concatenation of a single element:

$$\alpha \ list ::= \qquad \mathsf{NIL} \mid$$

$\mathsf{CON} \ \mathbf{of} \ \alpha \times \alpha \ list$

For convenience we introduce the abbreviations [] for the empty list NIL and x#xs for the concatenation  $\mathsf{CON}(x,xs)$ . The functions hd and tl return the head and the tail of a list, respectively, i.e. it holds hd(x#xs) = x and tl(x#xs) = xs. Moreover, we abbreviate concatenation of many elements, as for example of a#(b#(c#[])) by writing [a,b,c]. We denote the the size of a list xs by length(xs). Access to list element i is denoted by xs!i, where the head element is xs!0 = hd(xs). Updates of the ith list element to some value v is denoted by xs[i:=v].

Given a list of pairs, we may interpret the first element of each pair as a key and the second one as the data. We define a lookup for a given key id by  $xs?id \equiv snd(xs!(\min\{i \mid fst(xs!i) = id \land i < length(xs)\}))$ . Concatenation of two lists of the same type is denoted by xs@ys. Finally, we define an operator which returns for a given list a set containing all its elements. It is defined by  $set(xs) \equiv \{x \mid \exists i < length(xs). \ xs!i = x\}$ .

## Chapter 2

# Road Map

This thesis is composed of two parts: in the first part we report on the formal functional verification of device drivers, while in the second part we elaborate on the correctness of client/server software. The remainder of this chapter may be read as a manual to the thesis or as its summary, alternatively.

### 2.1 Formal Verification of Device Drivers

Part I is divided into two portions: First, we develop the extension of the language stack, which covers device semantics and enables the verification of drivers in the setting of traditional program logic (Chapter 3). Then, we leverage this stack to verify a hard disk driver and integrate the results into the overall kernel correctness (Chapter 4).

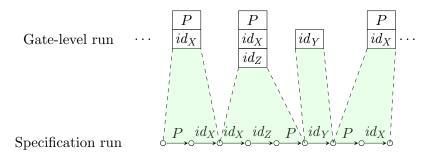

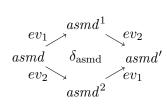

Our journey starts in Section 3.1 with the aim of defining and justifying a low-level programming model for device drivers running on the VAMP processor. Therefore, we first elaborate on the three levels of VAMP abstraction: VAMP gate-level, VAMP ISA and VAMP assembly. Subsequently, we introduce a general device model, and show how devices are embedded at each of the VAMP levels. At gate-level we encounter a lock-step model, in which all devices and the processor execute in parallel, whereas in the upper models granularity on time is lost. This loss is modeled by a non-deterministic oracle and interleaved semantics. Adjacent models of the VAMP are linked to each other via simulation theorems, which are used to propagate properties proven on abstract levels to lower levels. Most importantly, in this thesis, we are concerned with simulation between VAMP ISA with devices and VAMP assembly with devices and in the resulting software restrictions (Theorem 1).

Although we are arguing about a concurrent system, we want to use conventional verification technology—say verification condition generators for Hoare logic—to argue about (as large as possible) sequential portions of the interleaved computation. Therefore, in Section 3.2 we introduce a small reordering theory, which (i) provides us with theorems to embed reasoning about

the interleaved model into sequential programs and (ii) which simplifies to verify low-level drivers. We state several lemmas and theorems used to separate verification of processor and device computations (Theorems 2 and 3).

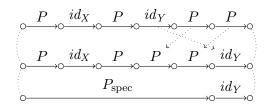

In Section 3.3 we describe the C0 small step semantics and outline the compiler correctness theorem (Theorem 4), which links C0 computations to the computations of the compiled code running on VAMP assembly. We proceed with extending compiler correctness to a target machine with device computations (Theorem 5). Basically, correctness follows from the fact that the compiled code never accesses devices and from the application of the reordering theory. Complier correctness imposes a set of conditions on the memory consumption of the target machine. Such conditions are of dynamic nature, i.e. they have to be discharged at each step of the computation. Hence, we verify a method to statically estimate the memory consumption of C0 code (Theorem 6).

In Section 3.4 we show how inline assembly (with no device access) can be embedded into C0 code, define an appropriate new semantics and state its soundness against VAMP assembly (Theorem 7). Subsequently, we extend C0 with inline assembly to allow device access. The new transition system enables us to reason completely sequentially on C0 code and separate the verification of assembly drivers for different devices. The soundness of this model against VAMP assembly is based on the reordering theory developed before (Theorem 8).

To capture the semantical effects of drivers and embed them into Hoarestyle reasoning, we introduce the concept of XCalls. XCalls are basically atomic state updates on the C0 machine and an arbitrary state extension, which is used to abstract from low-level entities (as e.g. devices). In Section 3.5 we formulate an adequate semantics of C0 with XCalls, define the notion of implementation correctness of an abstract call, and prove an extended compiler correctness theorem (Theorem 9). The proof is conducted by relying on the semantics for C0 with inline assembly accessing devices.

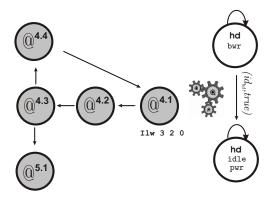

In Chapter 4 the obtained new and extended language stack is applied to verify a hard disk driver and embed the result into the verification process of the CVM kernel. We start in Section 4.1 by defining a formal model of the hard disk. Then, in Section 4.2 the assembly driver for writing memory pages is described and its correctness stated (Theorem 10). Verification is carried out by applying the reorder theory presented beforehand. Next, in Section 4.3 we embed the assembly driver into C0, specify it in terms of the XCall semantics and prove its correctness (Theorem 11). The verification is carried out by applying the XCall theory developed previously. Finally, we outline how this theorem is used in the context of the page-fault handler verification.

## 2.2 Verification of Client/Server Software

Part II is divided into two portions: First, we describe the formal model upon which the client/server software is implemented and introduce a verification methodology to deal with non-interfering system calls (Chapter 5). Then, we leverage this model and technique to specify the correctness of an RPC implementation and verify a simple math server (Chapter 6).

We start in Section 5.1 with a brief overview of the functionality of the simple operating system and by outlining its position in the Verisoft system stack. In Section 5.2, we specify a subset of Bogan's SOS\*, a distributed model of computation, describing the interactions of the simple operating system SOS with its user processes. Thereby, user processes are modeled in a quite abstract way such that they can be instantiated to model user programs in different programming languages. To be realistic, the model necessarily has to include inter process communication (IPC) and basic port mapper functionality. Furthermore, to be able to derive any useful termination properties, fairness of the scheduler has to be postulated on the model. In the SOS\* model, timeouts are restricted to finite and infinite timeouts.

Similar to the concurrent model of processor and devices, we deal with a distributed system. Desirably, here again, conventional programming logic should be used to argue about sequential portions of the distributed computation. For that purpose, in Section 5.3, we develop (similar to the reordering theory) a simple theory of non interfering system calls (Theorem 12).

In Section 6.1, we instantiate the user process model to C0 applications. However, pure C0 small step semantics is not sufficient to describe these applications: semantics of system call invocations have also to be formalized. We outline how to extend such small steps semantics for system calls like the portmapper- and IPC calls. This permits us to show that a service can indeed be looked up after it has been registered at the portmapper (Lemma 39). It seems very attractive to apply the concept of XCalls developed previously also to specify system calls. However, in contrast to the device model, our goal here, is not to hide all the interleaving in a single atomic step. This is not possible, since the concurrent interaction of the operating system and the processes should remain visible.

In Section 6.2, we show how to specify signatures of services in terms of C0 types.

Interface compilers generate from such signatures a library of external CO functions implementing the remote procedure call primitives RPCsend and RPCrecv. The implementation of these functions uses the (previously defined) IPC primitives. One has to be able to show termination, if timeouts are finite (Lemma 40). Furthermore, one has to show that matching RPCsend and RPCrecv calls either lead to a timeout or to a rendezvous situation and that, in the latter case, the data is correctly communicated (Lemma 41).

The RPC primitives RPCsend and RPCrecv as well as the portmapper calls

suffice to implement a wide variety of protocols. We demonstrate this in Section 6.5 for a simple example of an RPC client protocol.

A library, providing functions implementing the complete client protocol for calling remote procedures, can be generated by a compilation process for interfaces. For the functions generated by this library, one has to be able to show that they look up services and, in the case of success, eventually send calls to the server and receive answers (Theorem 13). Theorem 13, just like Lemma 41, is carefully phrased to reflect the fact that protocols may get stuck if some clients do not obey the required protocol.

Finally, in Section 6.6, we implement, with the given primitives, a simple Math Server. This server registers its services at the portmapper and then services remote procedure calls. If all clients adhere to the protocol, then one can show that the protocol never gets stuck and that remote procedure calls with infinite timeouts eventually get answers (Theorem 14).

# Part I

# Formal Function Verification of Device Drivers

## Chapter 3

# Extending the Language Stack

### 3.1 VAMP and Devices

The goal of this section is to develop a justified, low-level programming model for drivers.

The processor of choice in Verisoft is called **Verified Architecture Micro Processor** (VAMP). It has a non trivial design, supporting fix-point arithmetic, out-of-order execution, internal and external interrupts and two different execution modes: system and user mode. In the latter, memory access is subject to address translation. Devices are integrated to the VAMP by means of memory-mapped I/O.

We model the VAMP at three different levels of abstraction: (i) VAMP gate-level, which describes the gate-level implementation, (ii) VAMP ISA which is the corresponding instruction set architecture, and hence the specification model to VAMP gate-level, (iii) and VAMP assembly, which is intended to be a convenient layer for implementation and verification of low-level applications. It abstracts from certain aspects of lower layers which are irrelevant for most applications.

At each level, devices are modeled as finite state automata communicating with the processor and a not modeled external environment. However, the interaction model between the VAMP and the devices differs from level to level. At gate-level the processor and the devices are executed in lock-step, i.e. in each clock cycle each device and the processor take a transition. At VAMP assembly and VAMP ISA, devices and the processor are executed interleaved.

We start by elaborating on the computational models of the VAMP without devices. Subsequently, we introduce the general device model and show how devices are embedded. By establishing two simulation theorems between the adjacent models, properties shown for VAMP assembly with devices can be transferred to VAMP ISA with devices and finally to the gate-level implementation of the hardware. We conclude this section by outlining and discussing both simulations.

Note, that the models are introduced bottom-up, from a coarse overview of the gate-level implementation to a fine-grained assembly description, which will serve as the target language for driver verification.

The VAMP architecture is based on the DLX architecture [HP96] and was initially presented in [MP00]. An implementation of the VAMP has been formally verified in 2003 [BJK<sup>+</sup>03,BJK<sup>+</sup>06]. Since then, the VAMP has been extended with address translation and support for I/O devices [AHK<sup>+</sup>07, DHP05, TS08]. Details on the gate-level implementation of the VAMP and its verification can be found elsewhere [Tve09, TA08].

### 3.1.1 Gate-level Model

A configuration  $h \in C_h$  of the VAMP gate-level model consists of

- 32 bit registers, which are visible for the programmer. These are the program counters, the general purpose registers and the special purpose registers,

- additional 32 bit implementation specific registers, which are invisible for the programmer,

- a random access memory (RAM).

The VAMP is a pipelined machine with many stages supporting forwarding and out-of-order execution. For the embedding of devices two stages are of special interest (see Section 3.1.4): (i) the memory stage, in which store and write operations access the memory and (ii) the write-back stage, in which instructions are written back and interrupts become visible.

The transition function of the hardware takes as input the current configuration of the hardware and an external event vector representing interrupt signals of the connected devices. It returns the updated hardware configuration after one cycle.

### 3.1.2 Instruction Set Architecture

The instruction set architecture VAMP ISA fulfills two aims: (i) downwards it represents the specification for the gate-level hardware design, (ii) upwards it provides the system programmer with the model describing all visible components and behavior, including address translation and interrupt handling. In this section we only give an overview over the transition system. A full-blown description of VAMP ISA can be found in [MP00].

### **State Space**

Processor configurations are of the record type  $C_{isa}$ , which consists of the following fields:

$\mathsf{pc} \in \mathbb{B}^{32}$  The program counter.

$\mathsf{dpc} \in \mathbb{B}^{32}$  The delayed program counter (used to spec-

ify the delayed branch mechanism detailed in

[MP00]).

$\operatorname{\sf gpr} :: \mathbb{B}^5 \to \mathbb{B}^{32}$  . The general purpose register file.

$\mathsf{spr} :: \mathbb{B}^5 \to \mathbb{B}^{32}$  — The special purpose register file.

$\mathsf{mm} :: \mathbb{B}^{32} \to \mathbb{B}^8$  The byte addressable memory.

The VAMP can be run in two different modes: system and user mode. The current mode is encoded in the register MODE of the spr. In system mode, programs can directly access the memory and fully control the architecture via a number of privileged instructions. In user mode, memory accesses are subject to address translation and attempts to execute a privileged instruction will result in an exception.

### **Transitions**

The next state transition function of VAMP ISA is given by the function  $\delta_{isa}$ , which takes a configuration and an external event vector and returns the successor configuration. The external event vector is a 19 bit-string, indicating for each connected device whether it is currently raising an interrupt signal or not:

$$\delta_{isa} :: C_{isa} \times \mathbb{B}^{19} \to C_{isa}$$

A transition can be sketched as follows: First, it is checked whether the current configuration (together with the external event vector) is causing an interrupt (see below). If not, the transition function is defined by a case-split on the instruction to which the delayed program counter is pointing (or more precisely: to the word in the memory pointed at by the dpc and which is interpreted as instruction).

Except for instructions related to interrupt handling and address translation the semantics of the VAMP ISA instruction set is equivalent to the one of VAMP assembly, and therefore omitted here.

### **Interrupt Handling**

We distinguish two classes of interrupts: external and internal. External interrupts are caused by devices, and may be masked, i.e. disabled, by the processor by setting the special purpose register SR. This is used, for example, to ensure that an operating system kernel is never interrupted while running. Internal

interrupts may be caused due to the execution of an illegal instruction or a privileged instructions in user mode, overflows during arithmetic operations, page-faults (see address translation) and by a special trap-instruction Itrap (used e.g. to invoke kernel calls).

The VAMP reacts to non-masked interrupts by entering into system mode and continuing execution at address 0, the start of the interrupt service routine (ISR). Normally, user mode is re-entered, continuing execution at the interrupted location, by issuing the privileged instruction Irfe, which marks the end of the ISR.

### **Address Translation**

The VAMP provides a single-level address translation mechanism. The memory of the VAMP is partitioned into so called pages, small consecutive chunks of data. Each page has size 4K, i.e. 4096 bytes. A memory address can be interpreted as follows: some bits denote the page index and the remaining bits the byte index in that page. In user mode, virtual memory addresses are translated via a page table to physical addresses. A page table is simply a mapping from virtual to physical page indices. It consists of word-sized page table entries, each entry contains (i) a physical page index, (ii) a write-protection bit, denoting whether the page is allowed to be written, and (iii) a valid bit, denoting whether the page is currently available in main memory or not. This bit may be used by a paging algorithm (cf. Chapter 4) to indicate that the requested page is currently swapped to the hard disk. The page table used by the hardware for translation is identified by the special purpose registers (i) page table origin, PTO, denoting its base address in memory, and (ii) the page table length, PTL.

A virtual address lookup may trigger a so called page-fault interrupt. This happens, for example, if the virtual page index lies outside the page table or the requested page is marked to be not valid.

### 3.1.3 Assembly

The VAMP assembly model provides a handy programming model by abstracting some features of the machine model VAMP ISA. In short, these abstractions are:

- Data is represented as integers, while addresses are represented as naturals instead of bit-vectors in VAMP ISA.

- VAMP assembly has a uniform, linear memory with no address translation visible. Hence, the model can be used to capture, either the execution of system mode computations or the execution of virtualized memory machines (i.e., for which memory virtualization is already implemented).

- Neither external nor internal interrupts are visible in VAMP assembly.

This requires that all maskable interrupts are masked (i.e. the status register SR is set to zero) and that the execution of the VAMP assembly will not lead to any non-maskable interrupts.

- Instructions are no longer encoded as bit-vectors. Rather, an abstract data type encoding valid instructions is introduced. Correctness of instruction decoding has then to be shown once and for all.

### VAMP Assembly Configuration

The VAMP assembly configuration is of record type  $C_{asm}$  with five fields:

$pc :: \mathbb{N}$  The program counter.

$dpc :: \mathbb{N}$  The delayed program counter, modeling the

delayed branch mechanism.

$\mathsf{gpr} :: \mathbb{Z} \ \mathit{list}$  The general purpose register file, which is mod-

eled as a list of integers.

$spr :: \mathbb{Z} \ list$  The special purpose register file.

$mm :: \mathbb{N} \to \mathbb{Z}$  The main memory, which is a mapping from

memory addresses (naturals) to memory cells (of type integer). This memory is to be interpreted as word-addressable memory of words.

### Interpretation of Bit-Strings

In the underlying architecture data and addresses are represented as 32-bit strings. There are two ways to interpret these bit-strings, either as two's complement or as binary numbers.

In VAMP assembly we interpret data fields (memory and registers) as two's complement numbers and addresses as binary numbers. Thus, we type them as integers and naturals, respectively. We can switch between both interpretations by the two functions i2n and n2i:

$$i2n: \mathbb{Z} \to \mathbb{N}$$

$n2i: \mathbb{N} \to \mathbb{Z}$   $i2n(i) = \begin{cases} i+2^{32} & \text{if } i < 0 \\ i & \text{otherwise} \end{cases}$   $n2i(n) = \begin{cases} n-2^{32} & \text{if } n > 2^{31} \\ n & \text{otherwise} \end{cases}$

Since, the program is encoded in the main memory, instructions are also represented as integers. However, we translate these integers to the abstract data type  $instr_T$ . This translation is done by the function to-instr:

$$to\text{-}instr :: \mathbb{Z} \to instr_T$$

Not all integers (or corresponding bit-strings on the ISA) decode to meaningful instructions. Thus, for some instructions, the translation may be undefined, i.e. return with *undef*.

Similarly, we can interpret a memory region starting at address st with length l as a list of instructions by the following function:

$$to\text{-}instr\text{-}list::(\mathbb{N}\to\mathbb{Z})\times\mathbb{N}\times\mathbb{N}\to instr_T\ list$$

$$\begin{array}{lll} \textit{to-instr-list} & (m,st,0) &= [] \\ & (m,st,l) &= (\textit{to-instr}(m(st))) \# (\textit{to-instr-list}(m,st+1,l-1)) \\ \end{array}$$

By defining the transition system via a case distinction on the abstract data type  $instr_T$ , we no longer have to reason about instruction decoding, when proving correctness of assembly programs.

### Validity of States

Not all VAMP assembly configurations encode meaningful states. For example, a register content with a number larger than  $2^{31} - 1$  has no counterpart in hardware.

Therefore, we define the following two predicates to restrict the naturals and integers in the model to the domains of 32-bit binary numbers and 32-bit two's complement numbers.

The domain of 32-bit binary numbers and 32-bit two's complement numbers is defined by (cf. Notations):

$$asm\text{-}nat :: \mathbb{N} \to bool$$

$$asm\text{-}int :: \mathbb{N} \to bool$$

$$asm\text{-}nat(n) = n \in \{0, \dots, 2^{32} - 1\}$$

$$asm\text{-}int(i) = i \in \{-2^{31}, \dots, 2^{31} - 1\}$$

We call a VAMP assembly configuration *valid*, denoted by the predicate *valid-asm*, if the contents of the program counters, the register files and the memory obey the domain restrictions. Furthermore, the lists representing the register files must have 32 elements:

$$\begin{array}{l} valid\text{-}asm :: C_{asm} \rightarrow bool \\ \\ valid\text{-}asm(asm) \equiv \\ asm\text{-}nat(asm.\texttt{pc}) \\ \land \quad asm\text{-}nat(asm.\texttt{dpc}) \\ \land \quad (\forall ind < 32 . asm\text{-}int(asm.\texttt{gpr}!ind)) \\ \land \quad (\forall ind < 32 . asm\text{-}int(asm.\texttt{spr}!ind)) \\ \land \quad (\forall ad . asm\text{-}int(asm.\texttt{mm}(ad))) \\ \land \quad length(asm.\texttt{gpr}) = 32 \\ \land \quad length(asm.\texttt{spr}) = 32 \end{array}$$

### VAMP Assembly Transitions

The transition system of VAMP assembly is given by the next-step function:

$$\delta_{asm} :: C_{asm} \to C_{asm}$$

Given a configuration d it defines the successor state d' by a case distinction on the current instruction, that is the instruction to which the current delayed pc is pointing at:

$$current\text{-}instr :: C_{asm} \rightarrow instr_T$$

$$current\text{-}instr(asm) \equiv to\text{-}instr(asm.\mathsf{mm}(asm.\mathsf{dpc} \div 4))$$

We distinguish five kinds of instructions, whose semantics are described in the next paragraphs: (i) Arithmetical, logical and shift operations, (ii) memory operations, (iii) control operations, (iv) access to special purpose registers and, (v) interrupt related operations.

All instructions, except for control and interrupt, increment the delayed program counter by four (i.e. pointing to the next instruction) and set the new value of pc to the old one of the dpc:

$$inc ext{-}pc:: C_{asm} o C_{asm}$$

$$inc ext{-}pc(asm) \equiv asm[ ext{pc}:= asm. ext{dpc} +_{32} 4, \ ext{dpc}:= asm. ext{pc}]$$

In the following, we abbreviate states in which the program counters are incremented by  $asm_{inc} = inc - pc(asm)$ .

Arithmetic / Logical / Shift Operations The VAMP supports five types of arithmetic operations: addition and subtraction modulo 32, and the bitwise operations  $\wedge_{32}$ ,  $\vee_{32}$  and  $\otimes_{32}$ . For each operation two instructions are provided: either the second operand is a register content or it is the immediate constant of the instruction. Six shift operations are implemented: four logical and two arithmetic shifts. Moreover, the logical operators  $=,\neq,<,>,\geq$  and  $\leq$  are supported.

The table in Figure 3.1 gives the semantics of arithmetic and and shift instructions (note that we abbreviate asm.gpr!RS2 by RS2). The table in Figure 3.2 gives the semantics of logical instructions.

Memory Operations The VAMP supports eight different memory access instructions: five for reading data from memory into the gpr, and three for storing data from the gpr to the memory. The effect of the instructions differ in size (words, half-words and bytes) and offset of the data to read/store.

Memory operations have three parameters:

| Arithmetic | Operations |

|------------|------------|

|            |            |

| Tillimicole Operations |                  |     |  |

|------------------------|------------------|-----|--|

| Instruction            | 0                | OP2 |  |

| Iaddi RD RS i          | $+_{32}^{t}$     | i   |  |

| Isubi RD RS i          | $-\frac{t}{32}$  | i   |  |

| Iandi RD RS i          | $\wedge_{32}^t$  | i   |  |

| Iori RD RS i           | $\vee_{32}^t$    | i   |  |

| Ixori RD RS i          | $\otimes_{32}^t$ | i   |  |

| Iadd RD RS RS2         | $+_{32}^{t}$     | RS2 |  |

| Isub RD RS RS2         | ${32}^{t}$       | RS2 |  |

| Iand RD RS RS2         | $\wedge_{32}^t$  | RS2 |  |

| Ior RD RS RS2          | $\vee_{32}^t$    | RS2 |  |

| Ixor RD RS RS2         | $\otimes_{32}^t$ | RS2 |  |

Shift Operations

| Instruction     | 0                | OP2 |

|-----------------|------------------|-----|

| Isll RD RS1 RS2 | $<<_{32}^{t,l}$  | RS2 |

| Isrl RD RS1 RS2 | $>>_{32}^{t,l}$  | RS2 |

| Isra RD RS1 RS2 | $>>_{32}^{t,a}$  | RS2 |

| Islli RD rs sa  | $ <<_{32}^{t,l}$ | sa  |

| Isrli RD rs sa  | $>>_{32}^{t,l}$  | sa  |

| Israi RD rs sa  | $>>_{32}^{t,a}$  | sa  |

Figure 3.1: Semantics of Arithmetic and Shift Operations:  $asm' = asm_{inc} [\mathsf{gpr} := (asm.\mathsf{gpr} [RD := RS \circ OP2])]$

Logic Operations I OP2 = asm.gpr!RS2

| 01 % — worm.6pi1002 |                       |  |

|---------------------|-----------------------|--|

| Instruction         | 0                     |  |

| Iclr RD RS1 RS2     | $\lambda ab.0$        |  |

| Isgr RD RS1 RS2     | <                     |  |

| Iseq RD RS1 RS2     | =                     |  |

| Isge RD RS1 RS2     | $ $ $\leq$            |  |

| Isls RD RS1 RS2     | >                     |  |

| Isne RD RS1 RS2     | $\lambda ab.a \neq b$ |  |

| Isle RD RS1 RS2     | $\geq$                |  |

| Iset RD RS1 RS2     | $\lambda ab.1$        |  |

Logic Operations II OP2 = i

| $OI \ z = t$  |                       |

|---------------|-----------------------|

| Instruction   | 0                     |

| Iclri RD RS i | $\lambda ab.0$        |

| Isgri RD RS i | <                     |

| Iseqi RD RS i | =                     |

| Isgei RD RS i | $\leq$                |

| Islsi RD RS i | >                     |

| Isnei RD RS i | $\lambda ab.a \neq b$ |

| Islei RD RS i | $\geq$                |

| Iseti RD RS i | $\lambda ab$ .true    |

Figure 3.2: Semantics of Logical Operations:  $asm' = asm_{inc} [\mathsf{gpr} := (asm.\mathsf{gpr} [RD := RS \circ OP2])]$

$RS1 \in \mathbb{N}$  The register from / to which the memory data is stored / loaded.

$RS2 \in \mathbb{N}$  The register containing the memory source or destination address in memory.

$i \in \mathbb{N}$  Offset of the memory address.

The set of all memory operations are identified by the following two predicates is-store and is-load:

is-store ::  $C_{asm} \times \mathbb{N} \times \mathbb{N} \times \mathbb{N} \to bool$

```

\begin{aligned} is\text{-}store(asm,RS1,RS2,i) &\equiv \\ (\exists\,RS1,RS2,i \,. \\ &current\text{-}instr(asm) \in \{ &\text{Ilw RS1 RS2 i, Ilb RS1 RS2 i, Ilh RS1 RS2 i, } \\ &\text{Ilbu RS1 RS2 i, Ilhu RS1 RS2 i, } \\ &is\text{-}load :: \, C_{asm} \times \mathbb{N} \times \mathbb{N} \times \mathbb{N} \to bool \\ is\text{-}load(asm,RS1,RS2,i) &\equiv \\ (\exists\,RS1,RS2,i \,. \\ &current\text{-}instr(asm) \in \{ \text{Isb RS1 RS2 i, Ish RS1 RS2 i, Isw RS1 RS2 i} \} ) \end{aligned}

```

The effective address of store / load operations is computed as follows:

$ea :: C_{asm} \to \mathbb{N}$

$$ea(asm) \equiv \\ \begin{cases} i2n(asm.\mathsf{gpr}!RS2) +_{32} i2n(i) & \text{if} \quad is\text{-}store(asm,RS2,?,i) \lor \\ & \quad is\text{-}load(asm,RS2,?,i) \\ undef & \text{otherwise} \end{cases}$$

In the remainder of this article, only instructions for reading and writing complete words will be used. The semantics of these instructions is only defined if the memory address is well formed, i.e. it has to be in range and word aligned:

$$valid\text{-}ad :: \mathbb{N} \to bool$$

$$valid\text{-}ad(ad) = ad + 4 < 2^{32} \wedge 4 \text{ dvd } ad$$

We get for reading and writing words the following semantics:

In the following we use the predicates  $lw(asm) \equiv current-instr(asm) =$  Ilw??? and  $sw(asm) \equiv current-instr(asm) =$  Isw??? to indicate a load or store word instruction.

**Control** The VAMP supports six control instructions: two branch operations and four unconditional jumps. All of them have the same effect on the delayed program counter: asm'.dpc = asm.pc. Jumps are either relative or absolute, and may either save the incremented current pc to a predefined register L or not. The effects of the control instructions on the pc and possibly on

| Control Operations |                                                                                                    |                        |

|--------------------|----------------------------------------------------------------------------------------------------|------------------------|

| Instruction        | New Program Counter $pc_n$                                                                         | Save Register $data_n$ |

| Ibeqz R i          | $\begin{cases} asm.pc +_{32} i & asm.R = 0 \\ asm.pc +_{32} 4 & \mathbf{otherwise} \end{cases}$    | asm.gpr!L              |

| Ibnez R i          | $\begin{cases} asm.pc +_{32} i & asm.R \neq 0 \\ asm.pc +_{32} 4 & \mathbf{otherwise} \end{cases}$ | "                      |

| Ij i               | $asm.pc +_{32} i$                                                                                  | "                      |

| Ijr R              | i2n(asm.R)                                                                                         | "                      |

| Ijalr R            | i2n(asm.R)                                                                                         | $n2i(asm.pc +_{32} 4)$ |

| Ijal i             | $asm.pc +_{32} i$                                                                                  | "                      |

## Control Operations

Table 3.1: Control instructions

the gpr are summarized by the following formula, where the variables  $pc_n$  and  $data_n$  are defined in Table 3.1 (note that we abbreviate asm.gpr!R by asm.R):

$$asm' = asm[\mathsf{dpc} := asm.\mathsf{pc},$$

$$\mathsf{pc} := pc_n,$$

$$\mathsf{gpr} := asm.\mathsf{gpr}[\mathsf{L} := data_n]]$$

Move to/from spr The two instructions Imovs2i RD SA and Imovi2s SA RS copy data between a general purpose register and a special purpose register. Both instructions can only be executed in system mode. Otherwise no effect is visible in the assembly model:

$$\frac{current\text{-}instr(asm) = Imovs2i \ RD \ SA \qquad asm.spr!MODE = 1}{asm' = asm_{inc}[\mathsf{gpr} := asm.\mathsf{gpr}[RD := asm.\mathsf{spr!}(SA)]]}$$

$$\frac{current\text{-}instr(asm) = Imovs2i \ RD \ SA \qquad asm.\mathsf{spr!}MODE = 1}{asm' = asm_{inc}[\mathsf{spr} := asm.\mathsf{spr}[SA := asm.\mathsf{gpr!}(RD)]]}$$

**Interrupts** The VAMP supports two instructions dealing with interrupt handling. The first is Itrap, which triggers a trap interrupt, and the second is Irfe, which is invoked when returning from an interrupt handler. Since neither interrupt triggering, nor interrupt handling is modeled in VAMP assembly, also the corresponding instructions should not have any visible effects. Still, they have to be modeled and they may be part of a valid VAMP assembly program.

$$\frac{current\text{-}instr(asm) = Irfe}{asm' = asm} \qquad \frac{current\text{-}instr(asm) = Itrap?}{asm' = asm}$$

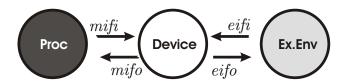

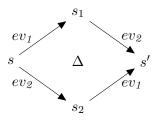

Figure 3.3: Interaction of device with processor and external Environment

## **VAMP Assembly Computations**

The function  $\Delta_{asm}$  denotes a t-step VAMP assembly computation. We have  $\Delta_{asm}(asm, t+1) = \Delta_{asm}(\delta_{asm}(asm), t)$  if t > 0 and asm otherwise.

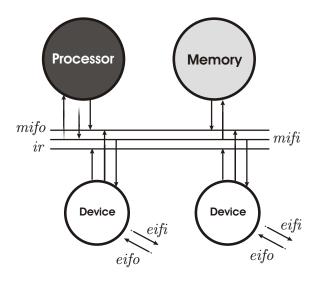

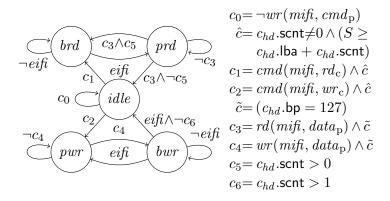

# 3.1.4 Integrating Devices

In this section we first introduce our general device model, then we sketch the device integration into the VAMP gate-level and VAMP ISA model, and finally present the desired programming model VAMP assembly with devices in detail.

## Modeling a Device

Devices are modeled as finite state transition systems interacting with the processor and with an external environment. The latter may be used, for example, to model user interaction or a network.

Communication with the processor is modeled via so called memory interface input, *mifi*, and output, *mifo*. The naming is relative to the viewpoint of the device, i.e. a *mifi* encodes a request of the processor to the device, and a *mifo* the corresponding answer of the device to the processor (see Figure 3.3).

A mift is of record type  $Mift_T$ , which has the following four fields:

$rd \in bool$  The read flag signals a read request of the processor.

$wr \in bool$  The write flag signals a read request of the processor.

$ad \in \mathbb{N}$  The address encodes the device port from / to which the processor wants to read / write.

$din \in \mathbb{N}$  In case of a write request, this field encodes the data (one word) to be written from the processor to the device. Note, that (in contrast to assembly) data is interpreted as a binary number.

We call the element ( $\mathsf{rd} = \mathsf{false}, \mathsf{wr} = \mathsf{false}, \mathsf{ad} = 0, \mathsf{din} = 0$ ) the idle mift and denote it with  $mifi_{\epsilon}$ . A memory output  $mifo \in Mifo_T$  of a device contains the result of a requested read input from the processor. This output encodes a word as natural, i.e.  $Mifo_T = \mathbb{N}$ . The interface to the external environment depends on the type of each device.