# Putting it all together – Formal Verification of the VAMP

### Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

Sven Beyer

sbeyer@cs.uni-sb.de

Saarbrücken, März 2005

Tag des Kolloquiums: 18.03.2005

Dekan: Prof. Dr. Jörg Eschmeier

Vorsitzender des Prüfungsausschusses: Prof. Dr.-Ing. Holger Hermanns

1. Berichterstatter: Prof. Dr. Wolfgang J. Paul

2. Berichterstatter: Prof. Dr. Wolfram Büttner

3. Berichterstatter: Prof. Bernd Finkbeiner, PhD

akademischer Mitarbeiter: Dr. Christian Lindig

Goodbye to you, my trusted friend.

We've known each other since we're nine or ten.

Together we climbed hills or trees.

Learned of love and ABC's,

skinned our hearts and skinned our knees.

— Terry Jacks, Seasons in the Sun

timshel—'Thou Mayest'

— John Steinbeck, East of Eden

Schieb' den Wal zurück ins Meer!

— Die Toten Hosen, Walkampf

### Danke

Dieser Abschnitt ist all denjenigen gewidmet, die ihr Scherflein zum Gelingen der vorliegenden Arbeit beigetragen haben.

Ich möchte zuallererst meinen Eltern danken, die mich während meiner gesamten Ausbildung in jedweder nichtwissenschaftlichen Weise gefördert haben.

Mein ganz besonderer Dank gilt auch Herrn Prof. Paul für die Vergabe des überaus spannenden und herausfordernden Themas und die wissenschaftliche Unterstützung meiner Promotion.

Ein dreifaches Hurrah und Prosit auch an das gesamte VAMP-Team für das Gelingen des Projekts.

Ein dickes Lob gebührt auch Werner Backes und meinen Freunden am Lehrstuhl, insbesondere Mark Hillebrand, Thomas In der Rieden, Christian Jacobi, Dirk Leinenbach und Jochen Preiß für das gute Lehrstuhl-Klima und zahlreiche fruchtbare Diskussionen sowie Bierbrauen, massierte Hähnchen, Doppelkopf-Abende und Kicker-Partien.

Und schließlich möchte ich auch Silvia Dorbach, Holger Herff und Christoph Schmidt herzlich danken für die unzähligen Abende in den letzten 15 Jahren, bei denen ich mich einfach vollständig zu Hause gefühlt habe.

### Abstract

In this thesis we describe the formal verification of a cache memory interface and its integration into a microprocessor called VAMP. The cache memory interface and the VAMP are modeled on the gate level and verified against their respective specifications, i.e., a dual-ported memory for the cache memory interface and the programmer's model of the VAMP.

The cache memory interface features separate instruction and data caches with write back policy for the data cache; the caches are connected to a unified physical memory accesses via a bus protocol with bursts. The VAMP is an out-of-order 32 bit RISC CPU with DLX instruction set, fully IEEE-compliant floating point units, and a memory unit with a cache memory interface. The VAMP also supports precise interrupts. The formal verification of the out-of-order algorithm and the floating point units of the VAMP is not subject of this thesis; we 'only' put all the different parts together to an overall correctness proof.

### Kurzzusammenfassung

In dieser Arbeit beschreiben wir die formale Verifikation eines Cache Memory Interfaces und dessen Integration in einen Mikroprozessor, den VAMP. Das Cache Memory Interface und der VAMP werden auf der Gatterebene modelliert und gegen ihre Spezifikation verifiziert, also einen Speicher mit zwei Zugriffsports für das Cache Memory Interface und das Programmiermodell des VAMP.

Das Cache Memory Interface besteht aus getrennten Instruktions- und Daten-Caches mit write-back Policy für den Daten-Cache. Die Caches sind mit einem vereinten physikalischen Speicher verbunden, auf den mittels eines Busprotokolls mit Bursts zugegriffen wird. Der VAMP ist eine out-of-order 32-bit RISC CPU mit DLX-Instruktionssatz, vollständig IEEE-konformen Fließkommaeinheiten und einer Speicher-Einheit mit einem Cache Memory Interface. Der VAMP unterstützt auch präzise Interrupts. Die formale Verifikation des out-of-order Algorithmus und der Fließkommaeinheiten des VAMP ist nicht Gegenstand dieser Arbeit; wir setzen lediglich die verschiedenen Teile zusammen zu einem Gesamt-Korrektheitsbeweis.

### Extended Abstract

In this thesis we report on the formal verification of a cache memory interface and its integration into the out-of-order microprocessor VAMP [BJK<sup>+</sup>03, BJK<sup>+</sup>05]. Both the implementation of the circuits and their verification are carried out in the theorem proving system PVS [OSR92]. The design of the cache memory interface was inspired by the textbook on computer architecture by Müller and Paul [MP00] while its verification is completely new. Note that the design also extends the work of Müller and Paul by integrating write back policy for the data cache.

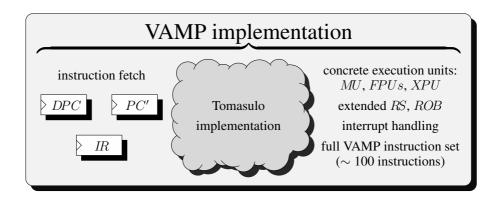

The VAMP is a pipelined out-of-order [Krö01] 32-bit RISC CPU with DLX instruction set, fully IEEE 754 [Ins85] compliant floating point units [Ber01, BJ01, Jac02a, Jac02b] for single- and double precision operations, a memory unit with a cache memory interface, delayed PC, and precise interrupts. The design and the formal verification of the Tomasulo [Tom67] out-of-order algorithm and the VAMP's floating point units and are based on the PhD-theses of Daniel Kröning [Krö01] and Christian Jacobi [Jac02a], respectively. We extend their work by actually verifying an implementation of the Tomasulo algorithm with the floating point units, adding instruction fetch and a memory unit, as well as by integrating precise interrupts into the proof of the VAMP.

The verification is split into three parts in a bottom-up fashion. As a first step, we develop a correctness criterion for simple caches called *cache consistency*. We take the cache implementations from [MP00] and formally verify these implementations to be consistent caches. In addition to the implementations proposed by [MP00], we give an implementation of a so-called fully associative cache and verify its consistency.

The second part of this thesis covers the formal verification of a cache memory interface. In particular, this cache memory interface consists of two caches for instruction fetch and data memory accesses, respectively. However, in this part, the caches are just black-boxed circuits fulfilling the above defined cache consistency. We define a correctness criterion for a cache memory interface. This criterion basically states that the cache memory interface behaves just like a dual-ported memory. We also describe the full implementation of the cache memory interface and its formal verification against its specification. In particular, since both caches are connected to a physical memory that is accessed with so-called bursts, this formal verification entails the full formalization of such a bus protocol which is completely new.

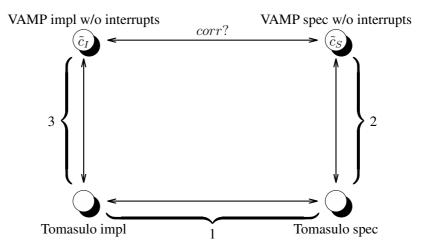

In the last step, we formally verify the overall correctness of the VAMP. For this level, the cache memory interface of the VAMP is just a black box with the correctness criterion verified in the previous step. We start with a definition of the programmer's model for the VAMP and a description of the VAMP implementation. The verification is then split into two sub-steps,

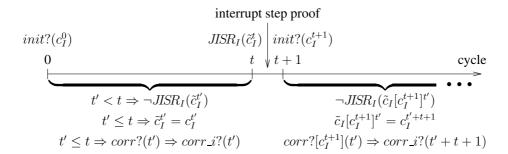

i.e., the correctness without interrupts and the correctness with interrupts. For the correctness without interrupts, we formally verify instruction fetch and the memory unit and instantiate the correctness of the Tomasulo algorithm by Kröning [Krö01]. In the last step, we add interrupts to the proof by decomposing arbitrary computations into interrupt-free parts, apply correctness without interrupts to these parts, and only investigate some additional proof into the cycles where an interrupts actually occurs.

All three steps together yield a formally verified gate-level implementation of the VAMP with interrupts and a cache memory interface with split instruction and data caches. The advantage of the different layers of abstraction corresponding to the above proof steps, however, is that is allows for concise and efficient reasoning, i.e., proofs are carried out only in the one small layer they logically belong to instead of the arguing over the huge overall implementation.

Together with the VAMP project team, we have also developed a translation tool [BJKL02] that takes our implementation of the VAMP from PVS and translates it to the hardware description language Verilog. This proves that real hardware can be synthesized from our implementation and we did not use any abstractions that cannot be represented by simple bits. The VAMP is currently running on a Xilinx FPGA on a PCI board at our institute.

### Zusammenfassung

Die vorliegend Arbeit behandelt die formale Verifikation eines Cache Memory Interfaces und seine Integration in den out-of-order Mikroprozessor VAMP [BJK+03,BJK+05]. Sowohl die Implementierung der Schaltkreise als auch ihre Verifikation erfolgen im Beweis-System PVS [OSR92]. Das Design des Cache Memory Interface wurde vom Rechnerarchitektur-Lehrbuch von Müller und Paul [MP00] inspiriert; seine Verifikation dagegen ist vollständig neu. Auch das Design erweitert die Arbeit von Müller und Paul durch die Integration von write-back Policy für den Daten-Cache.

Der VAMP is eine gepipelinete out-of-order [Krö01] 32-bit RISC CPU mit einem DLX-Instruktionssatz, vollständig IEEE 754 [Ins85] konformen Fließkommaeinheiten [Ber01, BJ01, Jac02a, Jac02b] für einfache und doppelte Genauigkeit, einer Speicher-Einheit mit einem Cache Memory Interface, delayed PC und präzisen Interrupts. Das Design und die formale Verifikation des Tomasulo [Tom67] out-of-order Algorithmus und der Fließkommaeinheiten des VAMP basieren auf den Dissertationen von Daniel Kröning [Krö01] und Christian Jacobi [Jac02a]. Wir erweitern die Arbeit der beiden indem wir tatsächlich eine Implementierung des Tomasulo Algorithmus mit Fließkommaeinheiten, den Instruction Fetch, die Memory-Einheit und die Integration von präzisen Interrupts verifizieren.

Die Verifikation gliedert sich bottom-up in drei Teile. Als erstes entwickeln wir ein Korrektheitskriterium für einfache Caches; wir nennen es Cache-Konsistenz. Wir nehmen die Cache-Implementierungen aus [MP00] und verifizieren formal, dass diese Implementierungen konsistente Caches sind. Zusätzlich zu den Implementierungen, die in [MP00] vorgeschlagen werden, geben wir die Implementierung eines sogenannten voll-assoziativen Caches an und verifizieren dessen Konsistenz.

Der zweite Teil dieser Arbeit ist der formalen Verifikation eines Cache Memory Interfaces gewidmet. Ein Cache Memory Interface besteht insbesondere aus zwei Caches für Instruction Fetch und Zugriffe auf den Datenspeicher. In diesem Teil sind die Caches aber nur black-boxed Schaltkreise, welche die oben definierte Cache-Konsistenz erfüllen. Wir definieren zunächst ein Korrektheitskriterium für ein Cache Memory Interface. Dieses Kriterium behauptet im wesentlichen, dass sich das Cache Memory Interface wie ein Speicher mit zwei Zugriffsports verhält. Wir beschreiben auch die vollständige Implementierung des Cache Memory Interfaces und dessen formale Verifikation gegen seine Spezifikation. Da beide Caches mit einem physikalischen Speicher verbunden sind, auf den mit sogenannten Bursts zugegriffen wird, benötigt diese formale Verifikation insbesondere die vollständige Formalisierung eines solchen Busprotokolls, was gänzlich neu ist.

Im letzten Schritt verifizieren wir die vollständige Korrektheit des VAMP formal. Auf diesem Level ist das Cache Memory Interface des VAMP einfach

eine Black Box mit dem Korrektheitskriterium, dass wir im vorhergehenden Schritt verifiziert haben. Wir geben zunächst eine Definition für das Programmiermodell des VAMP und eine Beschreibung der Implementierung des VAMP an. Die Verifikation gliedert sich dann in zwei weitere Schritte, nämlich die Korrektheit ohne und mit Interrupts. Wir verifizieren den Instruction Fetch und die Speicher-Einheit formal und instantiieren den Korrektheitsbeweis des Tomasulo-Algorithmus von Kröning [Krö01] für die Korrektheit ohne Interrupts. Im letzten Schritt erweitern wir den Beweis um Interrupts, indem wir beliebige Berechnungen in Interrupt-freie Abschnitte unterteilen, für die wir Korrektheit ohne Interrupts anwenden, und nur noch die Korrektheit derjenigen Takte beweisen, in denen tatsächlich ein Interrupt auftritt.

Mit allen drei Schritten zusammen erhalten wir eine formal verifizierte Implementierung des VAMP mit Interrupts und einem Cache Memory Interface mit getrennten Instruktions- und Daten-Caches auf der Gatterebene. Der Vorteil der verschiedenen Abstraktionsebenen liegt aber darin, dass sie eine präzise und effiziente Argumentation erlauben, denn Beweise werden nur in der kleinen Abstraktionsebene geführt, in die sie logisch auch gehören, anstatt über die riesige komplette Implementierung zu argumentieren.

Zusammen mit dem VAMP Projekt Team haben wir auch ein Übersetzungstool [BJKL02] entwickelt, das unsere VAMP Implementierung in PVS in die Hardware-Beschreibungssprache Verilog übersetzt. Dadurch wird bewiesen, dass wir in der Implementierung keine Abstraktionen benutzt haben, die sich nicht in einfachen Bits repräsentieren lassen. Der VAMP läuft zur Zeit auf einem Xilinx FPGA auf einer PCI-Karte an unserem Lehrstuhl.

# Contents

| 1 | Intr       | roduction                                              |

|---|------------|--------------------------------------------------------|

|   | 1.1        | The VAMP project                                       |

|   | 1.2        | Notation                                               |

|   | 1.3        | The PVS system                                         |

|   | 1.4        | Basic circuits                                         |

|   |            | 1.4.1 Multiplexer trees                                |

|   |            | 1.4.2 Parallel prefix or                               |

|   |            | 1.4.3 Encoder                                          |

|   | 1.5        | Proof decomposition                                    |

|   |            | 1.5.1 The memory interface layer                       |

|   |            | 1.5.2 The cache consistency layer                      |

| 2 | Cac        | hes 25                                                 |

|   | 2.1        | Definition                                             |

|   | 2.2        | Correctness criteria                                   |

|   | 2.3        | A direct-mapped cache                                  |

|   |            | 2.3.1 Correctness proof                                |

|   | 2.4        | A set-associative cache                                |

|   |            | 2.4.1 Correctness proof                                |

|   | 2.5        | A fully associative cache                              |

|   |            | 2.5.1 Correctness proof                                |

|   | 2.6        | Related work                                           |

| 3 | <b>A</b> c | ache memory interface 69                               |

|   | 3.1        | A bus protocol                                         |

|   |            | 3.1.1 Formal specification 69                          |

|   | 3.2        | Control automata                                       |

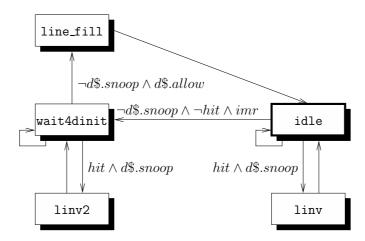

|   |            | 3.2.1 Instruction cache control                        |

|   |            | 3.2.2 Data cache control                               |

|   | 3.3        | Data paths                                             |

|   | 3.4        | Correctness proof                                      |

|   |            | 3.4.1 Valid cache input and bus protocol compliance 83 |

|   |            | 3.4.2 Consistency invariant                            |

xii CONTENTS

|   | 3.5 |           | Correct memory interface work |      |   |   |   |   |     |

|---|-----|-----------|-------------------------------|------|---|---|---|---|-----|

| 4 | The | VAMP      | microprocessor                |      |   |   |   |   | 111 |

|   | 4.1 |           | mer's model                   | <br> |   |   |   |   | 111 |

|   | 4.2 | Impleme   | entation                      | <br> |   |   |   |   | 118 |

|   |     | 4.2.1 T   | Comasulo algorithm            | <br> |   |   |   |   | 118 |

|   |     | 4.2.2 V   | AMP implementation            | <br> |   |   |   |   | 121 |

|   | 4.3 | Correctn  | iess criteria                 | <br> |   |   |   |   | 126 |

|   |     | 4.3.1 S   | cheduling functions           | <br> |   |   |   |   | 126 |

|   |     | 4.3.2 C   | Correctness Invariant         | <br> |   | • | • |   | 132 |

|   |     | 4.3.3 P   | Proof overview                | <br> |   |   |   |   | 133 |

|   | 4.4 | Correctn  | less without interrupts       | <br> |   |   |   |   | 138 |

|   |     | 4.4.1 I   | EEEf implementation           | <br> |   |   |   |   | 139 |

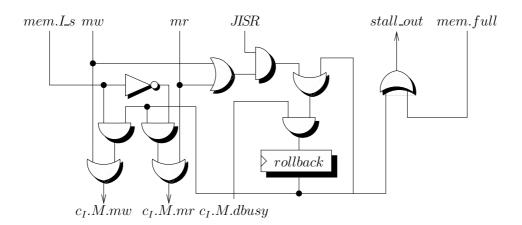

|   |     | 4.4.2 V   | AMP memory unit               | <br> |   |   |   |   | 140 |

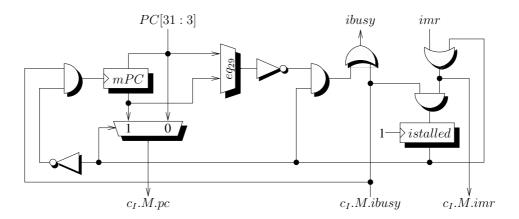

|   |     | 4.4.3 In  | nstruction fetch              | <br> |   |   |   |   | 149 |

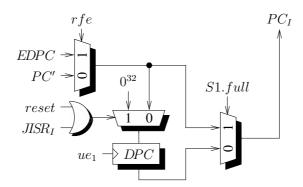

|   | 4.5 | Correctn  | less with interrupts          | <br> |   |   |   |   | 154 |

|   |     | 4.5.1 P   | Precise interrupts            | <br> |   |   |   |   | 154 |

|   |     | 4.5.2 C   | Overall correctness           | <br> |   |   |   |   | 158 |

|   | 4.6 | Impleme   | entation on an FPGA           | <br> |   |   |   |   | 159 |

|   | 4.7 | Related   | work                          | <br> | • |   |   | • | 161 |

| 5 | Con | clusion   |                               |      |   |   |   |   | 163 |

|   | 5.1 | Summar    | у                             | <br> |   |   |   |   | 163 |

|   | 5.2 | Discussio | on                            | <br> |   |   |   |   | 164 |

|   | 5.3 | Future w  | vork                          | <br> |   |   |   |   | 166 |

| A | VAN | IP instr  | ruction set                   |      |   |   |   |   | 169 |

| В | Lem | mas in I  | PVS                           |      |   |   |   |   | 175 |

# List of Figures

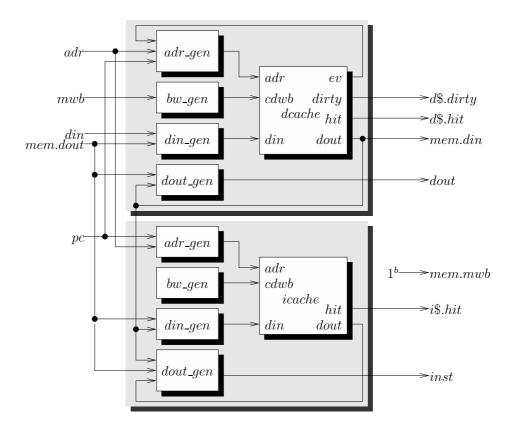

| 1.1  | Data paths of a memory interface                      |

|------|-------------------------------------------------------|

| 1.2  | Timing of the memory interface                        |

| 1.3  | Primitive memory interface performance                |

| 1.4  | Split cache memory interface performance              |

| 1.5  | Data paths of a cache memory interface                |

| 2.1  | Partitioning of an a-bit cache address                |

| 2.2  | LRU history updates                                   |

| 2.3  | Illustration of dirty consistency                     |

| 2.4  | Illustration of the continuous hit property           |

| 2.5  | Direct mapped cache                                   |

| 2.6  | Illustration of the proof of lemma 2.3.12 41          |

| 2.7  | Illustration of the continuous hit lemma              |

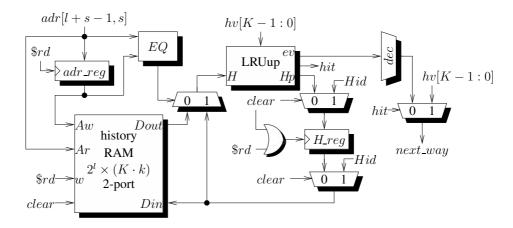

| 2.8  | K-way set-associative cache                           |

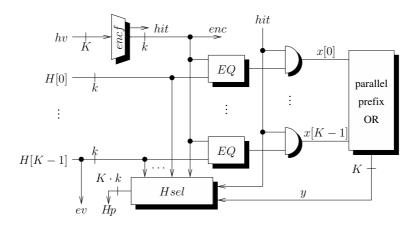

| 2.9  | LRU replacement circuit Repl                          |

| 2.10 | Next history computation $LRUup$                      |

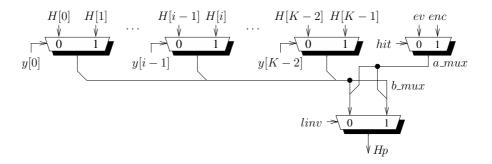

| 2.11 | Next history computation <i>Hsel</i>                  |

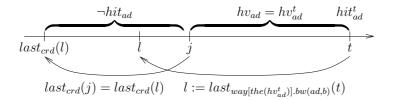

|      | Illustration of the claim of lemma 2.4.24 60          |

|      | Fully associative cache                               |

|      | Directory environment of a fully associative cache 65 |

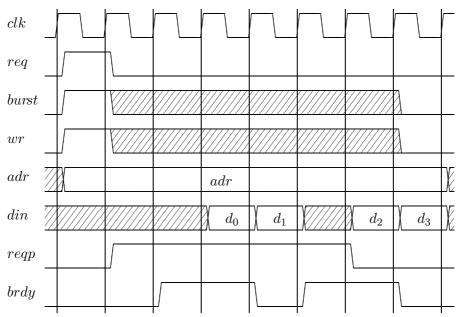

| 3.1  | 4-burst write timing diagram                          |

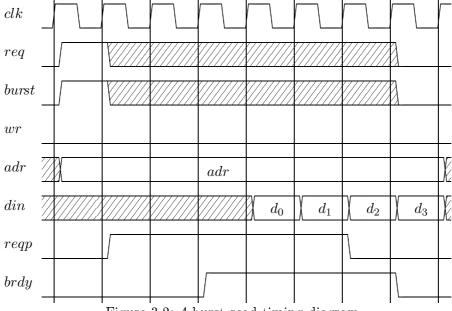

| 3.2  | 4-burst read timing diagram                           |

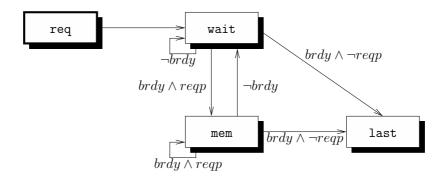

| 3.3  | Burst control FSD                                     |

| 3.4  | Instruction cache control FSD                         |

| 3.5  | Data cache control FSD                                |

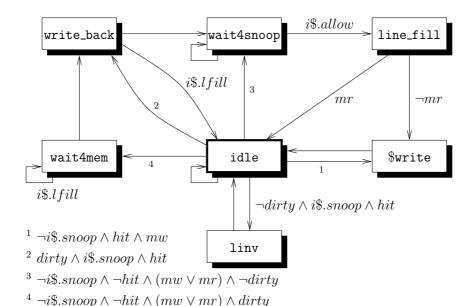

| 3.6  | Top-level data paths of the cache memory interface 81 |

| 3.7  | Forwarding circuit of the cache memory interface 82   |

| 3.8  | Correctness of the burst FSD                          |

| 3.9  | Correctness arguments for proof of lemma 3.4.23 98    |

| 3.10 | Correctness arguments for proof of lemma 3.4.28 104   |

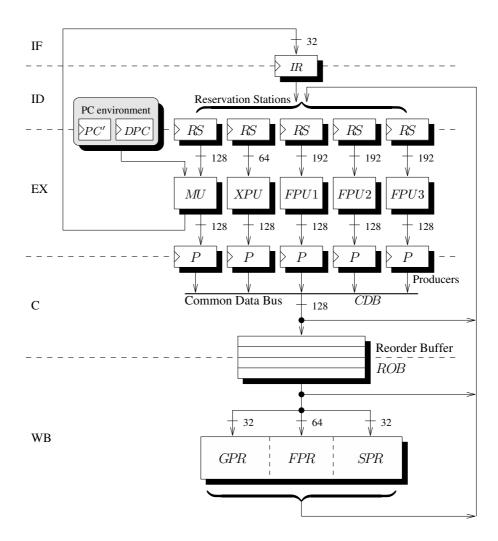

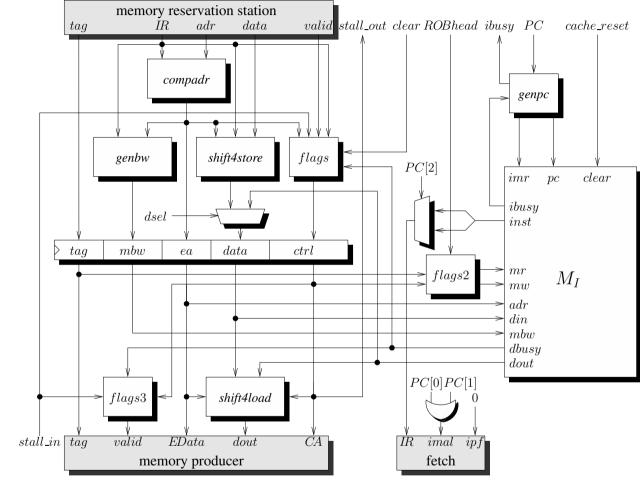

| 4.1  | The VAMP data paths                                   |

| 4.2  | Overview of the proof without interrupts              |

| 4.3 | VAMP implementation and Tomasulo implementation          | 135 |

|-----|----------------------------------------------------------|-----|

| 4.4 | Overview of the integration of interrupts into the proof | 138 |

| 4.5 | The VAMP memory unit                                     | 144 |

| 4.6 | Stabilizing circuit for a data access in the MU          | 146 |

| 4.7 | PC stabilizing circuit $genPC$                           | 147 |

| 4.8 | Fetch $PC$ implementation in the VAMP                    | 151 |

| 4.9 | Power-up sequence of the VAMP                            | 160 |

|     |                                                          |     |

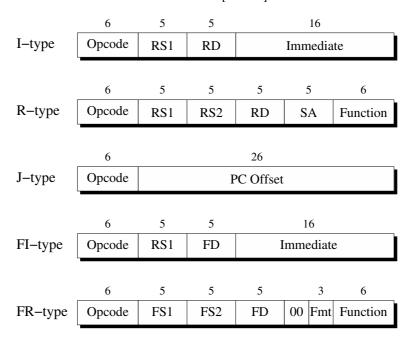

| Δ 1 | Instruction formats of the VAMP                          | 160 |

# List of Tables

| 1.1 | Interface between a CPU and a memory interface 17   |

|-----|-----------------------------------------------------|

| 1.2 | Description of input- and output signals of a cache |

| 2.1 | Cache parameters                                    |

| 4.1 | Supported interrupts in the VAMP                    |

| 4.2 | Special purpose registers of the VAMP               |

| 4.3 | Coding of the registers $RM$ and $IEEEf$            |

| A.1 | I-type instruction layout                           |

| A.2 | R-type instruction layout                           |

| A.3 |                                                     |

| A.4 |                                                     |

| A.5 | 01                                                  |

| A.6 |                                                     |

| B.1 | Overview of PVS contexts                            |

|     | Lemmas in PVS context basics                        |

| В.3 |                                                     |

| B.4 | Lemmas in PVS context history                       |

| B.5 | Lemmas in PVS context sa_cache                      |

| B.6 | Lemmas in PVS context fa_cache                      |

| B.7 | Lemmas in PVS context pipe_control                  |

| B.8 | Lemmas in PVS context pipe_control (continued) 179  |

|     | Lemmas in PVS context dlxtom                        |

# Chapter 1

## Introduction

'HAL, you have an enormous responsibility on this mission, in many ways perhaps the greatest responsibility of any single mission element. You're the brain, and central nervous system of the ship, and your responsibilities include watching over the men in hibernation. Does this ever cause you any lack of confidence?'

'Let me put it this way, Mr. Amor. The 9000 series is the most reliable computer ever made. No 9000 computer has ever made a mistake or distorted information. We are all, by any practical definition of the word, foolproof and incapable of error.'

This is a famous dialog from Stanley Kubrick's movie adaption [Kub68] of Arthur C. Clarke's '2001: A Space Odyssey' [Cla90]. HAL 9000 is a supercomputer who controls a human mission that aims at establishing contact with an alien species in the year 2001. Unfortunately, at some point, HAL decides to run amok and murder the human crew since, in his point of view, they hinder the success of the mission. However, a lone survivor of the crew succeeds in shutting down the higher functions of HAL's artificial intelligence and completes the mission alone.

HAL is obviously a highly complex computer system. Although no computer of his kind has ever made a mistake, this obviously does not guarantee absence of errors in the future. The 9000 series has been submitted to excessive testing, but due to HAL's complexity, simulation of all possible scenarios might just take several millennia. Hence, the only viable solution lies in formal verification. By formally verifying that HAL will under no circumstances consider his human crew 'expendable', one could have given the whole movie a new direction. This would have been very fortunate for the human crew, but on the other hand would rob us of a truly remarkable motion picture.

Seriously, however, there are many applications where microprocessors are employed in life-critical devices although these devices have not yet reached the complexity of HAL 9000. Consider, e.g., the medical sector,

nuclear power plants, cars, airplanes, or missiles. Due to the increasing complexity of these devices, the human effort invested in simulation increases exponentially, while simulation is less and less able to guarantee full security. Hence, formal verification more and more turns out to be the only alternative since the actual result of a formal verification is equivalent to a simulation of all possible cases, while it scales much better than simulation when putting the correctness of several modules together.

In this thesis, we consider the formal verification of a microprocessor called VAMP [BBJ<sup>+</sup>02, BJK<sup>+</sup>03, BJK<sup>+</sup>05] (Verified Architecture Microprocessor). Our particular focus lies on the cache memory interface of the VAMP which is based on the textbook of Müller and Paul [MP00, Chap. 6]. Our design extends their work by adding write back support to the data cache. All the proofs of the memory interface we present in this thesis are *new*.

The VAMP is a 32-bit RISC CPU with DLX instruction set. In addition to a memory unit with a cache memory interface, the VAMP features a Tomasulo [Tom67] out-of-order scheduler [Krö01], three floating point units [Ber01,BJ01,Jac02a,Jac02b], a fixed point unit, and precise interrupts. For the formal verification of the VAMP, we focus on the memory unit, instruction fetch, and precise interrupts in this thesis. We prove the overall VAMP implementation on the gate level correct with respect to a programmer's model that just executes one instruction in a step, i.e., we put all the different proofs together to one simple correctness statement. This correctness statement has also been formally verified in the theorem-proving system PVS [OSR92], i.e., all the proofs missing in this thesis due to lack of space have actually been carried out.

This thesis only deals with hardware verification. In order to formally verify the HAL 9000 system, however, both hardware and software correctness are needed. Hardware verification is just the first step and establishes a sound basis for software verification. In the discussion of future work, we will therefore give an outlook on the formal verification of software on top of verified hardware.

### Outline

In the remaining chapter 1 we introduce the VAMP project, basic notation and basic circuits, the PVS system, and the general proof decomposition approach of this thesis.

Chapter 2 to 4 correspond to the three verification steps we presented in the extended abstract. Chapter 2 gives implementations and correctness proofs of parameterized caches. We present the design and verification of a cache memory interface in chapter 3. Finally, in chapter 4 we put all the different parts together to a correctness proof of the overall VAMP implementation.

Chapter 5 summarizes the results, discusses advantages and drawbacks of

our approach, and gives directions for future work. Related work is discussed at the end the respective chapters.

### 1.1 The VAMP project

The work presented here is part of our institute's Verified Architecture Microprocessor (VAMP) project [JK00, BBJ<sup>+</sup>02, BJK<sup>+</sup>03, BJK<sup>+</sup>05] where we specified an instruction set architecture, implemented a complete microprocessor on the gate level, and formally verified it in PVS [OSR92] against its specification given by the instruction set architecture. The VAMP is a pipelined 32-bit RISC microprocessor based on the MIPS instruction set featuring precise interrupts, a Tomasulo scheduler [Krö01], a fixed point unit, a pipelined, fully IEEE 754 [Ins85] compliant FPU, and a cache memory interface.

The floating point units [Ber01, BJ01, Jac02a, Jac02b] support addition/subtraction, multiplication/division, and test and convert operation. Division is computed by a Newton-Raphson iteration with finite precision which requires a loop in the pipeline structure of the floating point unit. Both single and double precision operations are supported by the hardware; additionally, denormal numbers are handled in hardware. The full set of exceptions required by the IEEE standard is supported.

The fixed point unit consists of an ALU and a shifter; it also supports test operations. The memory unit supports byte, halfword, word, and double-word accesses of arbitrary, variable latency. In addition, load operations can be signed or unsigned. The cache memory interface supports write back for the data cache. In addition, instruction fetch is performed in the memory unit. Instruction and data cache are connected to a unified physical memory which is accessed via a bus protocol featuring bursts.

The VAMP supports maskable precise interrupts; return from the interrupt handler is achieved by means of an instruction. In addition, some interrupts re-execute the interrupted instruction while others continue with the next instruction. Typical supported interrupts are on illegal instruction or misaligned access, trap, and the interrupts provided by the floating point units as required by the IEEE standard.

Our hardware is written in a small subset of the PVS language. We use recursion and module instantiation for structured design, but the complete design can be unrolled down to the level of single bits and gates. This subset of the PVS language can be easily translated into common hardware description languages. For that purpose, we have developed a translation tool pvs2hd1 [BJKL02] that takes our PVS hardware description and translates it into gate-level Verilog HDL. This translation process basically consists of unrolling recursive PVS implementations like adders into non-recursive Verilog modules and flattening nested record data structures employed in

PVS to multiple bitvectors in Verilog. The tool pvs2hdl is not verified.

Additionally, we ported the gcc and the glibc to the VAMP architecture [Mey02]; again, no verification was done. The VAMP is currently running on a Xilinx FPGA on an PCI board in our institute [Lei02]. We had to add some unverified circuits on the FPGA, e.g., in order to bridge the gap between SD-RAM and our bus protocol and to allow for host access to the SD-RAM. The Xilinx synthesis software used to create the FPGA configuration is also not verified. However, the verified VAMP is running on the PCI board and we did not find a single bug after completing the VAMP's formal verification in PVS. All PVS specifications and proofs, the Verilog files, and the sources of pvs2hd1, gcc, and glibc are available at our web site.<sup>1</sup>

### 1.2 Notation

In this section we introduce some shorthand notations, properties of binary numbers, and a few basic concepts for reasoning about input sequences. For the whole thesis,  $\mathbb{N}$  denotes the natural numbers including 0 and  $\mathbb{N}^+ := \mathbb{N}\setminus\{0\}$ ; the set of integers, i.e.,  $\{\ldots, -1, 0, 1, \ldots\}$  is denoted by  $\mathbb{Z}$ . We start with some shorthand notation for sets.

**Definition 1.2.1** Let  $n, m \in \mathbb{Z}$  be numbers. We define the following integer intervals:

$$\begin{array}{cccc} [n:m] & := & [n,m] \cap \mathbb{Z} \\ ]n:m] & := & ]n,m] \cap \mathbb{Z} \\ [n:m[ & := & [n,m[ \cap \mathbb{Z} \\ ]n:m[ & := & ]n,m[ \cap \mathbb{Z} \\ & \mathbb{Z}_n & := & [0:n[ \\ & \mathbb{Z}_{\geq n} & := & \mathbb{N} \setminus \mathbb{Z}_n \end{array}$$

We now want to introduce bitvectors and arrays. We start with a standard definition of a word which is based on [LMW86].

**Definition 1.2.2** Let  $\Sigma \neq \emptyset$  be a set called **alphabet**. A word of length  $n \in \mathbb{N}$  over the alphabet  $\Sigma$  is a function  $a : \mathbb{Z}_n \to \Sigma$ . A word a is uniquely identified by the n-tuple of values  $(a(n-1), a(n-2), \ldots, a(0))$ . As a shorthand for this tuple, we also use  $a_{n-1}a_{n-2}\ldots a_0$  or just a[n-1:0]. The set  $\Sigma^n := \{a|a : \mathbb{Z}_n \to \Sigma\}$  is the set of all words of length n over  $\Sigma$ . We call  $\epsilon := \Sigma^0$  the empty word. The set of all words over  $\Sigma$  is given by

<sup>&</sup>lt;sup>1</sup>http://www-wjp.cs.uni-sb.de/projects/verification/

1.2. NOTATION 5

$\Sigma^* := \bigcup_{n \in \mathbb{N}} \Sigma^n$ . The **concatenation** of words is defined by

Instead of writing  $\cdot$  as infix operator, we also simple use a[n-1:0]b[m-1:0] for concatenation.

**Definition 1.2.3** A domain is an alphabet. An array is a word. We use the shorthand notation  $\mathbb{B} := \{0, 1\}$ . A bitvector of length n is an array of length n over the domain  $\mathbb{B}$ .

Note that the concept of arrays of length n over the domain D as words actually corresponds to the informal standard idea of arrays as containing n values over the domain D that are addressed by a[i] for  $i \in \mathbb{Z}_n$ . In addition, we can naturally have multi-dimensional arrays, e.g., by using  $\mathbb{B}^n$  as a domain of an array. Note also that we will not use  $\cdot$  for the concatenation of arbitrary arrays, but only for bitvectors since array concatenation is not a common operation.

By defining arrays as functions, we can also use  $\lambda$ -notation for arrays since  $\lambda$ -notation introduces unnamed functions. Note that we *only* use  $\lambda$ -notation as purely syntactical sugar for shorter notations, i.e., we do not employ real  $\lambda$ -calculus. Consider, e.g., a an array a of length m over the domain  $\mathbb{B}^n$ . A function upd(a,i,val) that updates index i of array a by val and leaves all other values untouched is defined by

$$upd(a, i, val)[j] := (j = i)? val : a[j], (j \in \mathbb{Z}_m).$$

Instead, with  $\lambda$ -notation, we only have a single equality instead of one equality per array index.

$$upd(a, i, val) := \lambda_{j \in \mathbb{Z}_m}(j = i)? val : a[j]$$

**Definition 1.2.4** Let  $n \in \mathbb{N}^+$  and  $a \in \mathbb{B}^n$ . We call

$$\langle a \rangle := \sum_{i=0}^{n-1} a[i] \cdot 2^i$$

the binary number represented by a. Note that  $\langle \cdot \rangle : \mathbb{B}^n \to \mathbb{Z}_{2^n}$  is bijective.<sup>2</sup> Thus, the function  $\operatorname{bin}_n := \langle \cdot \rangle^{-1}, \operatorname{bin}_n : \mathbb{Z}_{2^n} \to \mathbb{B}^n$  that returns the binary representation of a natural number is well founded.

Additionally, we identify the value 1 of a bit with the boolean value true and 0 with false for this thesis. This avoids tedious conversions on the bit level that are necessary in PVS.

$<sup>^2</sup>$ This property is formally verified in the PVS standard library bitvectors, cf. section 1.3.

**Proposition 1.2.5** Let  $a, b \in \mathbb{B}^n$ ,  $m \in \mathbb{Z}_n$ , and  $k \in \mathbb{Z}_{2^m}$ . The following statements hold:

- $\langle a \rangle \in \mathbb{Z}_{2^n}$

- $\langle a \rangle = \langle b \rangle \iff a = b$

- $\langle a \rangle = 2^m \cdot \langle a[n-1:m] \rangle + \langle a[m-1:0] \rangle$

- $\langle a \rangle \mod 2^m = k \iff \langle a[m-1:0] \rangle = k$

Proofs for these simple properties are available in the PVS bitvectors library we introduce in section 1.3 and are therefore omitted in this thesis. In our hardware implementations, we often use RAM in contrast to arrays. Therefore, we introduce the necessary notations in this section.

**Definition 1.2.6** For any  $a \in \mathbb{N}$  and  $d \in \mathbb{N}$ , a  $\mathbf{2^a} \times \mathbf{d}$ - $\mathbf{RAM}$  R is a function  $\mathbb{B}^a \to \mathbb{B}^d$  that maps any input address  $adr \in \mathbb{B}^a$  to its data value in R, denoted by R[adr].

Note that the only difference between an array and a RAM according to the above definition is in the type of the index variable, i.e., an array is always indexed by a natural number, whereas a RAM is indexed by a bitvector. Note that since a RAM is a function, we can also employ  $\lambda$ -notation for RAM. We now introduce some notation for the values of registers and signals in some cycle t.

**Definition 1.2.7** Let  $D_I$  a domain that does not contain RAM. A function  $inp : \mathbb{N} \to D_I$  is then called an **input signal** over the domain  $D_I$ . We use the shorthand notation  $inp^t$  for the value of inp in cycle t, i.e., inp(t).

Let  $c_{init}$  be some initial configuration over the domain  $D_c$ , inp some input signal over the domain  $D_I$ , and  $next_c: D_c \times D_I \to D_c$  a function that computes the next state of configuration c based on the current state and some input. We then denote the content of configuration c in cycle t given a starting configuration  $c_{init}$  with  $c[c_{init}]^t$ , i.e., we have

$$c[c_{init}]^{0} := c_{init}$$

$$c[c_{init}]^{t+1} := next_{c}(c[c_{init}]^{t}, inp^{t})$$

If we do not explicitly care for the starting configuration, but just assume an arbitrary, but fixed one, we also simply write  $c^t$ .

Let  $D_c$  and  $D_I$  be a configuration domain and an input signal domain, respectively. An **output signal** over the domain  $D_O$  is a function out:  $D_c \times D_I \to D_O$  and we once again denote the value of an output signal out in cycle t with out<sup>t</sup>, i.e., we have out<sup>t</sup> := out( $c^t$ , inp<sup>t</sup>). Note that we also write out[ $c_{init}$ ]<sup>t</sup> if we refer to a special initial configuration  $c_{init}$ .

1.2. NOTATION 7

In addition, we sometimes want to argue about some 'virtual' outputs, i.e., outputs given some hypothetical input  $in \in D_I$  instead of the concrete input  $inp^t$ . Therefore, we introduce the notation  $out_{in}^t := out(c^t, in)$ . Note that  $out_{inp^t}^t = out^t$  trivially holds.

Thus, we can now argue about signals and configurations in cycles and output signals based on hypothetical inputs. When arguing about the value of a signal s in different cycles, one often talks about the last time s was asserted or the next time s will be asserted. We now formalize these concepts and show a few simple properties. The corresponding PVS definitions and lemmas that we developed can be found in the context predicates.

**Definition 1.2.8** Let S be a signal over the domain D, P a predicate on D, and  $t \in \mathbb{N}$  a cycle. We introduce the shorthand notation  $P^t$  for  $P(S^t)$  and define a predicate indicating that P held in a cycle prior to t, i.e.,  $\exists_P^{last}(t) := \exists t' < t : P^{t'}$ , and a second predicate indicating that P holds in the present cycle or in a future cycle,  $\exists_P^{next}(t) := \exists t' \geq t : P^{t'}$ .

In case  $\exists_P^{last}(t)$  holds, we define the last cycle where P held, i.e.,  $last_P(t) := \max\{t' < t : P^{t'}\}$ . If  $\exists_P^{next}(t)$  holds, we define the next cycle where P holds as  $next_P(t) := \min\{t' \ge t : P^{t'}\}$ .

If it is clear from the context which predicate P is considered, we will abbreviate  $last_P(t)$  with last(t) and  $next_P(t)$  with next(t).

The following proposition collects a few trivial properties of the next and last definitions. The proofs are omitted in this thesis since they are very easy and very similar.

**Proposition 1.2.9** Let S, D, P, and t be like in Definition 1.2.8. Then the following properties hold:

- $\exists_P^{last}(t) \implies P^{last_P(t)} \land \forall t' \in ]last_P(t) : t[: \neg P^{t'}]$

- $\exists_P^{next}(t) \implies P^{next_P(t)} \land \forall t' \in [t : next_P(t)[: \neg P^{t'}]$

- $\bullet \ P^0 \wedge t > 0 \implies \exists^{last}_P(t)$

- $t' \ge t \land \exists_P^{last}(t) \implies \exists_P^{last}(t')$

- $\bullet \ t' \leq t \wedge \exists_P^{next}(t) \implies \exists_P^{next}(t')$

- $t' \le t \wedge P^{t'} \implies \exists_P^{last}(t) \wedge last_P(t) \ge t'$

- $t' \ge t \wedge P^{t'} \implies \exists_P^{next}(t) \wedge next_P(t) \le t'$

- $t' \ge t \land \exists_P^{last}(t) \implies last_P(t') \ge last_P(t)$

- $t' \le t \land \exists_P^{next}(t) \implies next_P(t') \le next_P(t)$

- $t' \in ]last_P(t):t] \implies last_P(t) = last_P(t')$

As an example for the use of the definition of *last*, we introduce the following simple lemma about register values which we will use often when arguing about the value in some register or RAM.

**Lemma 1.2.10** Let  $R_{init}$  be an initial configuration over the domain D,  $R_{ce}$  a signal over the domain  $\mathbb{B}$ , and  $R_{in}$  a signal over the domain D. We then define the content of register R in cycle  $t \in \mathbb{N}$  as follows:

$$R^{0} := R_{init}$$

$$R^{t+1} := \begin{cases} R_{in}^{t} & \text{if } R_{ce}^{t} \\ R^{t} & \text{otherwise} \end{cases}$$

For any cycle  $t \in \mathbb{N}$ , it holds that

$$R^{t} = \begin{cases} R_{in}^{last}_{Rce}(t) & \text{if } \exists_{Rce}^{last}(t) \\ R_{init} & \text{otherwise} \end{cases}$$

where we identify the boolean signal  $R_{ce}$  with a predicate that holds iff  $R_{ce}$  is asserted.

**Proof:** We show the claim by induction on t.

Induction base  $(\mathbf{t} = \mathbf{0})$ : By definition, we have  $R^0 = R_{init}$  which concludes the claim since  $\exists_{R_{ce}}^{last}(0)$  never holds.

**Induction step**  $(t \rightarrow t + 1)$ : By definition, we have

$$R^{t+1} := \begin{cases} R^t_{in} & \text{if } R^t_{ce} \\ R^t & \text{otherwise} \end{cases}$$

We now split cases on the value of  $R_{ce}^t$ .

- 1. If  $R_{ce}^t$  holds, we have  $R^{t+1} = R_{in}^t$ . In this case,  $\exists_{R_{ce}}^{last}(t+1)$  trivially holds and also  $last_{R_{ce}}(t+1) = t$  which concludes this case of the claim.

- 2. If  $R_{ce}^t$  does not hold, we trivially have  $R^{t+1} = R^t$  and  $\exists_{R_{ce}}^{last}(t+1) = \exists_{R_{ce}}^{last}(t)$ . With the induction hypothesis for  $R^t$ , this yields

$$R^{t+1} = \begin{cases} R_{in}^{last_{R_{ce}}(t)} & \text{if } \exists_{R_{ce}}^{last}(t+1) \\ R_{init} & \text{otherwise} \end{cases}$$

Note that in case of  $\neg \exists_{R_{ce}}^{last}(t+1)$ , we have  $R^{t+1} = R_{init}$  which concludes the proof. Let therefore  $\exists_{R_{ce}}^{last}(t+1)$  hold. We then have  $last_{R_{ce}}(t+1) = last_{R_{ce}}(t)$ . Thus, we get  $R^{t+1} = R^{last_{R_{ce}}(t+1)}$  which finishes the proof.

### 1.3 The PVS system

The Prototype Verification System [OSR92], abbreviated PVS, is an interactive theorem prover developed at SRI International. PVS features powerful decision procedures for natural numbers and a bitvectors library [BMSG96] that is the basis for our hardware implementations. Basic PVS bitvector types are bit which equals  $\mathbb{B}$  as defined in the previous section and bvec[n] for  $\mathbb{B}^n$ . Concatenation and bit extraction operators are defined in analogy to the concepts introduced in the previous section. In addition, the binary number represented by a bitvector is computed by a function bv2nat and the inverse is given by nat2bv. The library contains several simple lemmas about bitvectors which we just refer to in this thesis without giving a proof transcript like proposition 1.2.5.

Since bitvectors and arrays are also functions in PVS, the usage of  $\lambda$ -expressions in modelling bitvectors and arrays is natural. Note that PVS actually has to distinguish between  $\mathbb{B}$  and  $\mathbb{B}^1$  which we will not do in this thesis for the sake of readability.

The modeling of combinational hardware is straightforward in PVS, i.e., we employ functions which are possibly recursive and  $\lambda$ -expressions on the bitvector, array, or RAM types. You can basically take the design of the encoder in section 1.4.3 and just copy it to PVS while replacing  $\mathbb{B}^n$  with bvec[n] and get the actual PVS implementation.<sup>3</sup> The same basically holds true for the specification; you only have to replace the functions bin and log by their PVS-counterparts.

Modeling of clocked circuits, however, is not as straightforward as for combinational circuits. This stems from the fact that we use a functional subset of the PVS language for hardware modeling and therefore, we have no global state-holding variables which would correspond to registers. Hence, we just model a next-state function that maps the current configuration and some input to the successor configuration and, potentially, some output. The state and output of the system in cycle t given an input sequence up to cycle t can then be defined recursively based on the next state function just as we introduced in definition 1.2.7.

The interactive theorem prover PVS features all the standard techniques used in paper-and-pencil proofs, i.e., skolemization, case distinctions, induction, application of lemmas, and instantiation of suitably quantified formulas, while it unfortunately lacks an 'obvious' button that solves the numerous subgoals we will just declare to be 'obvious' in this thesis. However, since we actually completed the formal verification in PVS, we *know* that all the subgoal we declare as 'obvious' in this thesis really are obvious, although some effort might have been necessary in order to convince PVS of that fact.

<sup>&</sup>lt;sup>3</sup>Note that in this translation step, you have to take care of the distinction of  $\mathbb{B}$  and  $\mathbb{B}^1$  by PVS, e.g., you may have to add a  $\lambda$ -expression in order to convert a single bit into a bitvector.

On the other hand, in the one case in several dozens or so when PVS really was right and a subgoal was not 'obvious', we will present the details that defied obviousness in this thesis.

In summary, it is basically possible to translate any paper-and-pencil proof presented in this thesis into a formal PVS proof while keeping the proof structure we presented. Note that most of the proofs for this thesis have been developed directly in PVS and we just present a sanitized paper-and-pencil version of these proofs.

### 1.4 Basic circuits

In this section, we verify the correctness of various basic circuits that we will use as macros later on. We have already reported the verification of decoders, adders, equality-tester, and similar circuits in [BJK01]. Since we just use these macros and their proofs, we will not go into detail here apart from giving definitions. Instead, we will focus on additional macros like encoders and multiplexer trees.

**Definition 1.4.1** Let  $n \in \mathbb{N}^+$ . We then define the following parametrized circuits:

• An **n-ortree** is a circuit computing the function

$$or_n: \mathbb{B}^n \to \mathbb{B}, or_n(a) := \exists i \in \mathbb{Z}_n : a[i].$$

• An **n-equality-tester** is a circuit computing the function

$$eq_n: \mathbb{B}^n \times \mathbb{B}^n \to \mathbb{B}, eq_n(a,b) := (a = b).$$

• An **n-decoder** is a circuit computing the function

$$dec_n: \mathbb{B}^n \to \mathbb{B}^{2^n}, dec_n(a) := \lambda_{i \in \mathbb{Z}_{2^n}}(\langle a \rangle = i).$$

• An **n-adder** is a circuit computing the function

$$add_n: \mathbb{B}^n \times \mathbb{B}^n \times \mathbb{B} \to \mathbb{B}^{n+1}, \ add_n(a,b,c) := bin_{n+1}(\langle a \rangle + \langle b \rangle + \langle c \rangle).$$

• An **n-incrementer** is a circuit computing the function

$$inc_n: \mathbb{B}^n \to \mathbb{B}^{n+1}, inc_n(a) := bin_{n+1}(\langle a \rangle + 1).$$

We will just use the above specifications in all the proofs where the corresponding macros appear in our design. However, an implementation of, i.e., a decoder or an equality-tester together with a correctness proof is available in our PVS tree.

### 1.4.1 Multiplexer trees

**Definition 1.4.2** For  $n \in \mathbb{Z}_{\geq 2}$ ,  $m \in \mathbb{N}^+$ , an **n-muxtree** is a circuit computing the function

$$mux_n: (\mathbb{B}^m)^n \times \mathbb{B}^{\lceil \log n \rceil} \to \mathbb{B}^m, \ mux_n(A, b) := A[\langle b \rangle]$$

for any  $b \in \mathbb{B}^{\lceil \log n \rceil}$  with  $\langle b \rangle < n$ .

For  $n \in \mathbb{N}^+$ ,  $m \in \mathbb{N}^+$ , an **n-muxtree** with unary select is a circuit computing a function  $mux\_us_n : (\mathbb{B}^m)^n \times \mathbb{B}^n \to \mathbb{B}^m$  that fulfills for any Array A of size n over the Domain  $\mathbb{B}^m$ ,  $b \in \mathbb{B}^n$ , and any  $j \in \mathbb{Z}_n$

$$(b = \lambda_{i \in \mathbb{Z}_n}(j=i)) \implies mux\_us_n(A,b) = A[j].$$

**Lemma 1.4.3** For  $n \in \mathbb{N}$ ,  $m \in \mathbb{N}^+$ , the circuit  $MUX_{2^n} : (\mathbb{B}^m)^{2^n} \times \mathbb{B}^n \to \mathbb{B}^m$  defined by

$$\begin{array}{rcl} \mathit{MUX}_{2^{0}}(A,b) &:= & b[0]? \, A[1] : A[0] \\ \mathit{MUX}_{2^{n+1}}(A,b) &:= & b[n]? \, \mathit{MUX}_{2^{n}}(\lambda_{i \in \mathbb{Z}_{2^{n}}} A[2^{n}+i], b[n-1:0]) : \\ & & \mathit{MUX}_{2^{n}}(\lambda_{i \in \mathbb{Z}_{2^{n}}} A[i], b[n-1:0]) \end{array}$$

is a  $2^n$ -muxtree according to definition 1.4.2.

**Proof:** We show the claim  $MUX_{2^n}(A, b) = A[\langle b \rangle]$  by induction on n. **Induction base**  $(\mathbf{n} = \mathbf{0})$ : We have  $MUX_{2^0}(A, b) = b[0]?A[1] : A[0]$  which obviously equals  $A[\langle b \rangle]$ .

Induction step  $(\mathbf{n} \to \mathbf{n} + \mathbf{1})$ : Let  $MUX_{2^n}(A', b') = A'[\langle b' \rangle]$  for all A', b' according to induction hypothesis. We then have by definition

$$MUX_{2^{n+1}}(A, b) = b[n]? MUX_{2^n}(\lambda_{i \in \mathbb{Z}_{2^n}} A[2^n + i], b[n-1:0]):$$

$MUX_{2^n}(\lambda_{i \in \mathbb{Z}_{2^n}} A[i], b[n-1:0])$

By applying the induction hypothesis twice, we get

$$MUX_{2n+1}(A,b) = b[n]? A[2^n + \langle b[n-1:0] \rangle] : A[\langle b[n-1:0] \rangle]$$

With Proposition 1.2.5, this easily leads to

$$MUX_{2^{n+1}}(A,b) = A[\langle b \rangle]$$

which concludes the claim.

**Lemma 1.4.4** For  $n \in \mathbb{N}^+$ ,  $m \in \mathbb{N}^+$ , the circuit  $MUX\_us_n : (\mathbb{B}^m)^n \times \mathbb{B}^n \to \mathbb{B}^m$  defined by

$$MUX\_us_n(A,b) := \lambda_{i \in \mathbb{Z}_m} or_n(\lambda_{j \in \mathbb{Z}_n} A[j][i] \wedge b[j])$$

is an n-muxtree with unary select according to definition 1.4.2.

**Proof:** Let  $n \in \mathbb{N}+$ ,  $m \in \mathbb{N}+$ ,  $k \in \mathbb{Z}_n$  and  $b := \lambda_{i \in \mathbb{Z}_n}(k=i)$ . We then have to show MUX  $us_n(A,b) = A[k]$ . We start with the definition from lemma 1.4.3, i.e.,

$$MUX\_us_n(A, b) = \lambda_{i \in \mathbb{Z}_m} or_n(\lambda_{j \in \mathbb{Z}_{2^n}} A[j][i] \wedge b[j]).$$

By definition 1.4.1 for  $or_n$  we have

$$MUX\_us_n(A, b) = \lambda_{i \in \mathbb{Z}_m} \exists j \in \mathbb{Z}_n : A[j][i] \land b[j].$$

By replacing  $b = \lambda_{j \in \mathbb{Z}_n}(k = j)$ , we simply get

$$MUX \ us_n(A,b) = \lambda_{i \in \mathbb{Z}_m} A[k][i].$$

This concludes the claim since  $A[k] = \lambda_{i \in \mathbb{Z}_m} A[k][i]$ .

### 1.4.2 Parallel prefix or

**Definition 1.4.5** For  $n \in \mathbb{N}^+$ , an **n-parallel prefix or** is a circuit computing the function  $pp_n: \mathbb{B}^n \to \mathbb{B}^n$ ,

$$pp_n(a) := \lambda_{i \in \mathbb{Z}_n} \bigvee_{j=0}^{j \le i} a[j].$$

**Lemma 1.4.6** For  $n \in \mathbb{N}^+$ , we set  $m := \lfloor n/2 \rfloor$ ,  $a' := \lambda_{l \in \mathbb{Z}_m} a[2 \cdot l + 1] \vee a[2 \cdot l]$ , and define a circuit  $PP_n$  recursively by

$$\int a[0] \qquad l = 0$$

$$PP_{n}(a) := \lambda_{l \in \mathbb{Z}_{n}} \begin{cases} a[0] & l = 0 \\ PP_{m}(a')[(l-1)/2] & l > 0 \land odd?(l) \\ PP_{m}(a')[l/2 - 1] \lor a[l] & l > 0 \land even?(l) \end{cases}$$

Note that we use the predicates odd? and even? for odd and even integers, respectively. The circuit  $PP_n$  thus defined is a parallel prefix or according to definition 1.4.5.

**Proof:** We prove the claim  $PP_n(a) = \lambda_{i \in \mathbb{Z}_n}(\bigvee_{j=0}^{j \leq i} a[j])$  by induction on n. Induction base (n = 1): For n = 1, we have  $PP_1(a) = a = \bigvee_{i=0}^{j \le 0} a[j]$ which concludes the induction base.

**Induction step**  $(n \to n+1)$ : We set  $m := \lfloor (n+1)/2 \rfloor$  and additionally  $a' := \lambda_{l \in \mathbb{Z}_m}(a[2 \cdot l + 1] \vee a[2 \cdot l])$ . Note that the induction hypothesis guarantees  $PP_m(a') = \lambda_{i \in \mathbb{Z}_m}(\bigvee_{j=0}^{j \leq i} a'[j])$ . We then have by definition

$$PP_{n+1}(a) = \lambda_{l \in \mathbb{Z}_n} \begin{cases} a[0] & l = 0 \\ PP_m(a')[(l-1)/2] & l > 0 \land odd?(l) \\ PP_m(a')[l/2 - 1] \lor a[j] & l > 0 \land even?(l) \end{cases}$$

Applying the induction hypothesis yields

$$PP_{n+1}(a) = \lambda_{l \in \mathbb{Z}_n} \begin{cases} a[0] & l = 0\\ \bigvee_{j=0}^{j \le (l-1)/2} a'[j] & l > 0 \land odd?(l)\\ \bigvee_{j=0}^{j \le l/2-1} a'[j] \lor a[l] & l > 0 \land even?(l) \end{cases}$$

Expanding the definition of a', we get

$$PP_{n+1}(a) = \lambda_{l \in \mathbb{Z}_n} \begin{cases} a[0] & l = 0 \\ \bigvee_{j=0}^{j \le (l-1)/2} (a[2 \cdot j + 1] \vee a[2 \cdot j]) & l > 0 \wedge odd?(l) \\ \bigvee_{j=0}^{j \le l/2 - 1} (a[2 \cdot j + 1] \vee a[2 \cdot j]) \vee a[l] & l > 0 \wedge even?(l) \end{cases}$$

In all three cases, this equals the desired result, i.e.,

$$PP_{n+1}(a) = \lambda_{l \in \mathbb{Z}_n} (\bigvee_{j=0}^{j \le l} a[j])$$

which concludes the induction step.

### 1.4.3 Encoder

**Definition 1.4.7** For  $n \in \mathbb{Z}_{\geq 2}$ , an **n-encoder** is a circuit computing a function  $enc_n : \mathbb{B}^n \to \mathbb{B}^{\lceil \log n \rceil}$  that fulfills for any  $a \in \mathbb{B}^n$  and  $j \in \mathbb{Z}_n$

$$(a = \lambda_{i \in \mathbb{Z}_n}(j=i)) \implies enc_n(a) = bin_{\lceil \log n \rceil}(j)$$

**Lemma 1.4.8** For  $n \in \mathbb{N}^+$ , we define a circuit  $encf_{2^n} : \mathbb{B}^{2^n} \to \mathbb{B}^{n+1}$  recursively by

$$encf_{2^{n}}(a) := (a[1] \lor a[0]) \cdot a[1]$$

$encf_{2^{n+1}}(a) := (lo[n] \lor hi[n]) \cdot \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} hi[n] & i = n \\ lo[i] \lor hi[i] & otherwise \end{cases}$

$with \ lo := encf_{2^{n}}(a[2^{n} - 1 : 0])$

$and \ hi := encf_{2^{n}}(a[2^{n+1} - 1 : 2^{n}])$

This circuit is an extended encoder, i.e.,  $encf_{2^n}(a)[n-1:0] = enc_{2^n}(a)$  and  $encf_{2^n}(a)[n] = or_{2^n}(a)$ .

The implementation in the above lemma is taken from [MP95]. In order to verify this lemma, we first show the following two propositions.

**Proposition 1.4.9** For  $n \in \mathbb{N}^+$  and  $a \in \mathbb{B}^n$ , the highest bit of  $encf_{2^n}$  computes just an n-ortree, i.e.,  $encf_n(a)[n] = or_n(a)$ .

Since the recursive definition of  $encf_{2^n}(a)[n]$  exactly equals the definition of an or-tree, this proposition is trivially verified.

**Proposition 1.4.10** For  $n \in \mathbb{N}^+$ , it holds that  $encf_{2^n}(0^{2^n}) = 0^{n+1}$ .

**Proof:** One part of this proposition, i.e.,  $encf_{2^n}(0^{2^n})[n] = 0$  is already given by proposition 1.4.9. For the remaining bits, we show the claim  $encf_{2^n}(0^{2^n})[n-1:0] = 0^n$  by induction on n.

**Induction base** (n = 1): We have by definition  $encf_{2^1}(00)[0] = 0$  which concludes the induction base.

**Induction step**  $(\mathbf{n} \to \mathbf{n} + \mathbf{1})$ : Let  $encf_{2^n}(0^{2^n})[n-1:0] = 0^n$  hold by induction hypothesis. By definition, we have

$$encf_{2^{n+1}}(0^{2^{n+1}})[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} encf_{2^n}(0^{2^n})[n] & i = n \\ encf_{2^n}(0^{2^n})[i] \lor encf_{2^n}(0^{2^n})[i] \end{cases}$$

otherwise

We conclude the claim with the induction hypothesis and with proposition 1.4.9.

With these two propositions, we are now finally able to prove lemma 1.4.8 correct

**Proof:** (of Lemma 1.4.8) Let  $n \in \mathbb{N}^+$ ,  $j \in \mathbb{Z}_{2^n}$ , and  $a := \lambda_{i \in \mathbb{Z}_{2^n}} (j = i)$ . Note that  $\lceil \log 2^n \rceil = n$  trivially holds. We show  $encf_{2^n}(a)[n-1:0] = bin_n(j)$  by induction on n.

**Induction base** (n = 1): We have two cases depending on the value of j.

- 1. For j = 0, we have  $encf_{2^1}(01)[0] = a[1] = 0 = bin_1(0)$  which concludes the claim.

- 2. For j=1, we have  $encf_{2^1}(10)[0]=a[1]=1= bin_1(1)$  which also concludes the claim.

Thus the claim holds for the induction base.

Induction step  $(\mathbf{n} \to \mathbf{n} + \mathbf{1})$ : Let  $j \in \mathbb{Z}_{2^{n+1}}$ ,  $a := \lambda_{l \in \mathbb{Z}_{2^{n+1}}} (j = l)$ , and  $encf_{2^n}(\lambda_{i \in \mathbb{Z}_{2^n}}(j'=i))[n-1:0] = bin_n(j')$  hold by induction hypothesis for any  $j' \in \mathbb{Z}_{2^n}$ . We then have by definition

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} hi[n] & i = n \\ lo[i] \lor hi[i] & \text{otherwise} \end{cases}$$

with  $lo := encf_{2^n}(a[2^n - 1:0])$  and  $hi := encf_{2^n}(a[2^{n+1} - 1:2^n])$  just as in lemma 1.4.8. By replacing hi, lo, and a on the right hand side, we get

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} encf_{2^n}(\lambda_{l \in \mathbb{Z}_{2^n}}(j=l+2^n))[n] & i=n \\ encf_{2^n}(\lambda_{l \in \mathbb{Z}_{2^n}}(j=l))[i] \lor & \text{otherwise} \\ encf_{2^n}(\lambda_{i \in \mathbb{Z}_{2^n}}(j=l+2^n))[i] \end{cases}$$

Depending on the value of j, we now distinguish two cases.

1. For  $j \in \mathbb{Z}_{2^n}$ , we have  $\lambda_{l \in \mathbb{Z}_{2^n}} (j = l + 2^n) = 0^{2^n}$  and thus, we can apply proposition 1.4.10 in order to get

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} 0 & i = n \\ encf_{2^n}(\lambda_{l \in \mathbb{Z}_{2^n}}(j=l))[i] & \text{otherwise} \end{cases}$$

We now define j' := j and apply the induction hypothesis. This yields

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} 0 & i = n \\ \operatorname{bin}_n(j')[i] & \text{otherwise} \end{cases}$$

Since  $j' \in \mathbb{Z}_{2^n}$ , we have  $\sin_{n+1}(j')[n] = 0$ , and thus the claim is concluded by  $encf_{2^{n+1}}(a)[n:0] = 0 \cdot \sin_n(j') = \sin_{n+1}(j') = \sin_{n+1}(j)$ .

2. For  $j \geq 2^n$ , the arguments are similar. We have  $\lambda_{l \in \mathbb{Z}_{2^n}}(j=l) = 0^{2^n}$ , and apply propositions 1.4.10 and 1.4.9 and definition 1.4.1 in order to get

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} \exists l \in \mathbb{Z}_{2^n} : j = l+2^n & i = n \\ encf_{2^n}(\lambda_{l \in \mathbb{Z}_{2^n}}(j=l+2^n))[i] & \text{otherwise} \end{cases}$$

Since  $j \in [2^n : 2^{n+1}[$ , we define  $\mathbb{Z}_{2^n} \ni j' := j-2^n$  and thus, we have  $(\exists l \in \mathbb{Z}_{2^n} : (j=l+2^n)) = 1$ . We apply the induction hypothesis in order to get

$$encf_{2^{n+1}}(a)[n:0] = \lambda_{i \in \mathbb{Z}_{n+1}} \begin{cases} 1 & i = n \\ bin_n(j')[i] & \text{otherwise} \end{cases}$$

Since  $j \in [2^n : 2^{n+1}[$ , we have  $bin_{n+1}(j)[n] = 1$ , and thus the claim is concluded by  $encf_{2^{n+1}}(a)[n : 0] = 1 \cdot bin_n(j') = bin_{n+1}(j)$ .

We now trivially extend the encoder to input widths that are not a power of 2.

**Definition 1.4.11** For  $n \in \mathbb{Z}_{\geq 2}$ , we set  $k := \lceil \log n \rceil$ . We extend the definition of encf from lemma 1.4.8 by

$$encf_n(a) := encf_{2k}(0^{2^k - n} \cdot a).$$

This extended *encf* circuit trivially fulfills the correctness criteria presented in lemma 1.4.8, i.e., if  $a = \lambda_{i \in \mathbb{Z}_n} (i = j)$  for some  $j \in \mathbb{Z}_n$ , we have

$$encf_n(a)[k] = or_n(a)$$

$encf_n(a)[k-1:0] = bin_k(j)$

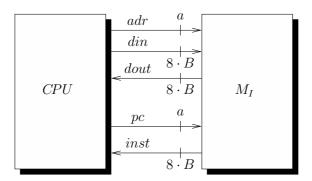

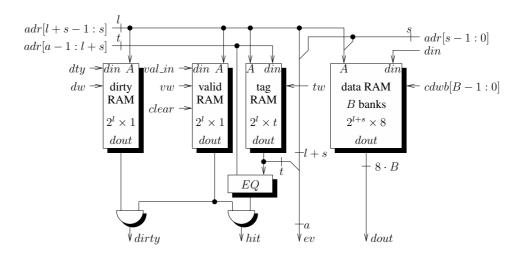

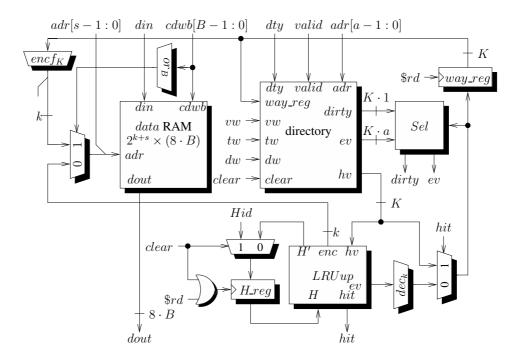

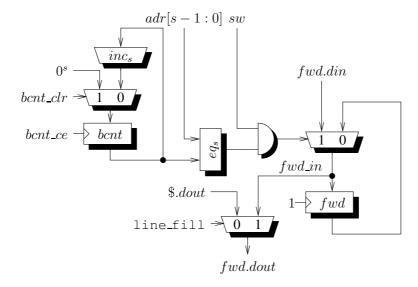

Figure 1.1: Data paths of a memory interface

### 1.5 Proof decomposition

We now want to give an overview on how the overall correctness proof of the VAMP with its cache memory interface is structured hierarchically. This proof decomposition allows for concise arguments while abstracting away all the information that is not needed for a proof. In particular, we will introduce the layers of a memory interface and a consistent cache in the following sections.

For the remaining chapter, let  $B \geq 1$  be the number of bytes stored in a single memory location, and let  $a \geq 1$  be the number of bits used in addressing the memory. Thus, a data word w consists of B bytes, i.e.,  $w \in \mathbb{B}^{8 \cdot B}$ , and our memory contains  $2^a \cdot B$  bytes. As a first step, we introduce the memory interface layer. The overall correctness proof of the VAMP will exclusively use this layer for any memory access.

### 1.5.1 The memory interface layer

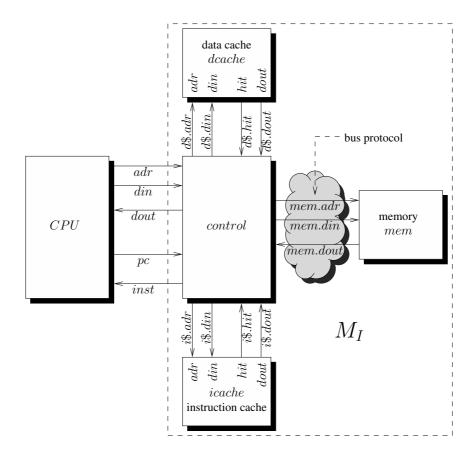

**Definition 1.5.1** A memory interface for a pipelined microprocessor is a circuit with inputs and outputs according to table 1.1; its data paths are depicted in figure 1.1.

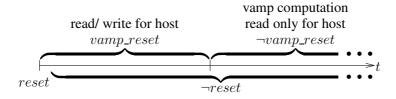

We call the CPU output to the memory interface **valid** if there is only an initial clear, any data or instruction access is stalled by an active dbusy or ibusy, respectively, and the read- and write signals on the data port are never raised simultaneously. Formally, we have

- $\forall t \in \mathbb{N} : clear^t = (t = 0)$

- $\bullet \ \forall t \in \mathbb{N}^+ : \neg mw^t \vee \neg mr^t$

- $\forall t \in \mathbb{N}^+ : (mr^t \vee mw^t) \wedge dbusy^t \implies \{adr, din, mw, mr, mwb\}^{t+1} = \{adr, din, mw, mr, mwb\}^t$

- $\forall t \in \mathbb{N}^+ : imr^t \wedge ibusy^t \implies \{pc, imr\}^{t+1} = \{pc, imr\}^t$

| Signal                    | Description                                  |  |  |  |  |

|---------------------------|----------------------------------------------|--|--|--|--|

| Memory interface input    |                                              |  |  |  |  |

| adr[a-1:0]                | word address of the data access              |  |  |  |  |

| $din[8 \cdot B - 1 : 0]$  | data word to be written                      |  |  |  |  |

| mw                        | signals data write access                    |  |  |  |  |

| mr                        | signals data read access                     |  |  |  |  |

| mwb[B-1:0]                | selects bytes of the data word to be written |  |  |  |  |

| pc[a-1:0]                 | word address of the instruction access       |  |  |  |  |

| imr                       | signals instruction read access              |  |  |  |  |

| clear                     | initializes memory interface                 |  |  |  |  |

| Memory interface output   |                                              |  |  |  |  |

| dbusy                     | signals pending data access                  |  |  |  |  |

| $dout[8 \cdot B - 1 : 0]$ | read data on finished data access            |  |  |  |  |

| ibusy                     | signals pending instruction access           |  |  |  |  |

| inst                      | read data on finished instruction access     |  |  |  |  |

Table 1.1: Interface between a CPU and a memory interface

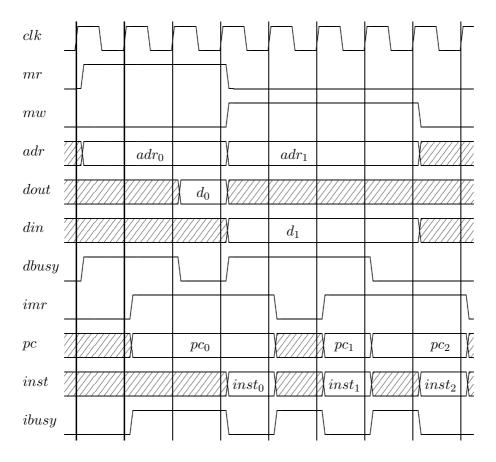

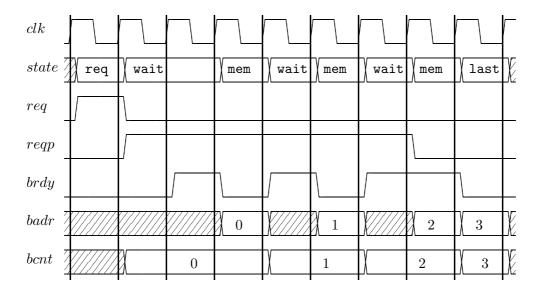

The timing in our memory interface is simple. The CPU starts a data request in a cycle t by raising  $mr^t$  for a read or  $mw^t$  for a write. The address of the request is  $adr^t$ , and in case of a write,  $din^t$  holds the data to be written and  $mwb^t$  contains the byte enables for the single bytes in  $din^t$ . All these signals keep their value until in a cycle  $t' \geq t$ ,  $dbusy^{t'}$  is lowered. In case of a read access, the data returned on  $dout^{t'}$  is the requested data.

Similarly, an instruction read request is started in a cycle t by an active  $mr^t$ . The address  $pc^t$  remains stable until in a cycle  $t' \geq t$ ,  $ibusy^{t'}$  is lowered. The data output  $inst^{t'}$  is the requested instruction data. Instruction and data request may be arbitrarily interleaved. This is illustrated in figure 1.2.

We call a memory interface with valid input from a CPU *correct* if it is both live and consistent. Liveness means that any access to the memory interface eventually terminates, and consistency means that any read access yields the expected data. The following definition formalizes these concepts.

**Definition 1.5.2** Let  $init\_mem \in (\mathbb{B}^{8 \cdot B})^{2^a}$  be the initial memory content of a memory interface. For any  $w \in \mathbb{B}^{8 \cdot B}$  and b < B, we use the shorthand notation  $|w|_b = w[8 \cdot b + 7 : 8 \cdot b]$  for the projection of word w to its b-th byte.

We introduce a parameterized predicate on the memory interface I/O by

$$M_I.bw(ad,b) := (ad = adr) \land mw \land mwb[b] \land \neg dbusy$$

in order to capture a write to byte b of address ad and define the memory

Figure 1.2: Timing of the memory interface

content  $M_I$  in cycle  $t \in \mathbb{N}^+$  recursively as follows:

$$\begin{array}{rcl} M_I^1 &:= & init\_mem \\ \left| M_I^{t+1}[\langle ad \rangle] \right|_b &:= & \begin{cases} \left| din^t \right|_b & \text{ if } M_I.bw(ad,b)^t \\ \left| M_I^t[\langle ad \rangle] \right|_b & \text{ otherwise} \end{cases} \end{array}$$

We call a memory interface **correct** iff on valid input from the CPU according to definition 1.5.1, the following conditions hold  $\forall t \in \mathbb{N}^+$ :

- 1.  $mr^t \wedge \neg dbusy^t \implies dout^t = M_I[\langle adr^t \rangle]^t$  (data cache consistency)

- 2.  $imr^t \wedge \neg ibusy^t \implies inst^t = M_I[\langle pc^t \rangle]^t$  (instruction cache consistency)

- 3.  $\exists_{\neg dbusy}^{next}(t)$  (data cache liveness)

- 4.  $\exists_{\neg ibusy}^{next}(t)$  (instruction cache liveness)

Thus, on concurrent read- and write accesses to the same address in the memory interface, there are two possible outcomes. Either the instruction read access terminates strictly after the write access and returns the correct data after the execution of the data write access, or it terminates in the same cycle or before the write and returns the old memory content. Both scenarios are equally possible in a correct memory interface.

Additionally, we note that according to lemma 1.2.10, the following equation trivially holds:

$$\left|M_{I}^{t}[\langle ad \rangle]\right|_{b} = \begin{cases} \left|din^{last}_{M_{I}.bw(ad,b)}(t)\right|_{b} & \text{if } \exists_{M_{I}.bw(ad,b)}^{last}(t) \land \\ & last_{M_{I}.bw(ad,b)}(t) > 0 \\ \left|init\_mem[\langle ad \rangle]\right|_{b} & \text{otherwise} \end{cases}$$

$$(1.1)$$

### A cache memory interface

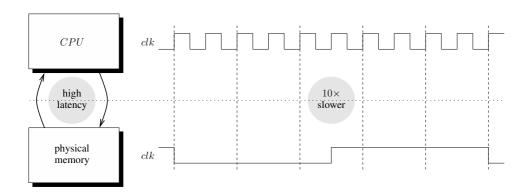

The CPU clock in modern microprocessors runs at about ten times the frequency of the memory clock. Furthermore, typical main boards support only dynamic memory, i.e., SD-RAM or DDR-RAM. This results in an access latency of several slow memory cycles which in turn is equivalent to a latency of several dozens of fast CPU cycles. On the other hand, an ideal CPU accesses the memory at least once per cycle for the fetch of a new instruction. For memory instructions, we have two accesses. In case of super-scalar architectures, multiple instructions are actually fetched per cycle. Clearly, a naive implementation of a memory interface yields unbearably bad performance. Figure 1.3 illustrates this scenario.

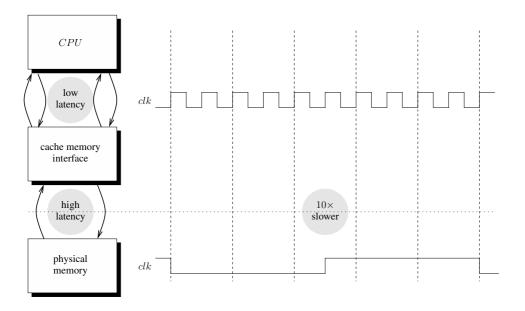

Therefore, so-called *caches* are introduced in a memory interface. A small but fast memory called cache is added between CPU and main memory. Ideally, this cache uses the full CPU clock thus allowing for one cache access per CPU cycle as depicted in figure 1.4.

Figure 1.3: Primitive memory interface performance

Figure 1.4: Split cache memory interface performance

Figure 1.5: Data paths of a cache memory interface

If the memory access can be handled by the cache, for example a read access to a memory location currently held in the cache, the slow main memory access is avoided in favour of a fast cache access. This type of access is called a hit. If, on the other hand, the cache does not hold the desired data, it is loaded from the main memory and stored in the cache for possible further use. We call this a miss. Clearly, a miss performs no better than a memory access without any cache. Since a cache memory interface shows a performance superior to that of a simple memory interface only in case of a hit, the so-called hit rate of the cache becomes an important factor, i.e., the number of hits divided by the total number of cache accesses. This hit rate depends on the cache size, the code executed on the CPU, and several other factors. Common cache memory interface architectures have been shown to achieve hit rates of 95% and more on typical benchmark applications; hence, the additional cost for adding hardware caches usually pays off.

| Signal                    | Description                                          |

|---------------------------|------------------------------------------------------|

| Input                     |                                                      |

| adr[a-1:0]                | memory word address                                  |

| $din[8 \cdot B - 1 : 0]$  | data word input for cache data memory                |

| cdwb[B-1:0]               | byte write signals for data word input               |

| vw                        | write enable for <i>valid</i> part of directory      |

| $val\_in$                 | data input for valid part of directory               |

| tw                        | write enable for tag part of directory               |

| dty                       | data input for dirty part of directory               |

| dw                        | write enable for dirty part of directory             |

| \$rd                      | initiates any cache access                           |

| clear                     | invalidates all the data in the cache                |

| Output                    |                                                      |

| hit                       | signals valid data on $dout$ for input address $adr$ |

| $dout[8 \cdot B - 1 : 0]$ | cache data output on address $adr$ in case $hit = 1$ |

| dirty                     | signals dirty data for input address $adr$           |

| ev[a-1:0]                 | signals eviction address in case $dirty = 1$         |

Table 1.2: Description of input- and output signals of a cache

### 1.5.2 The cache consistency layer

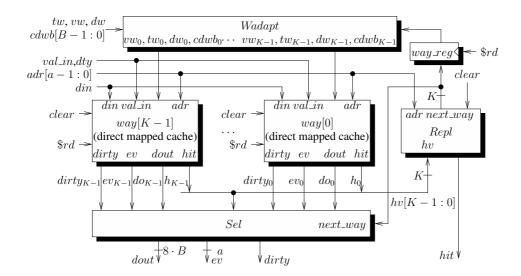

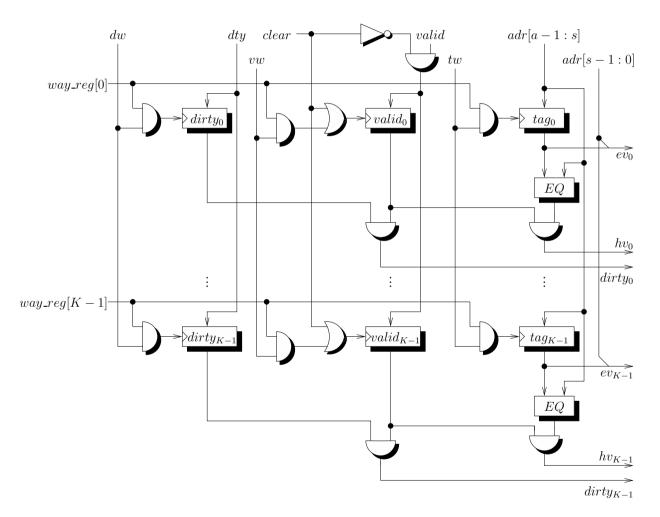

In a pipelined microprocessor, there are up to two memory accesses per CPU cycle. Therefore, two separate caches are used in order to implement a cache memory interface, an instruction cache and a data cache. This allows for two simultaneous memory accesses per CPU cycle. Thus, in case the caches produce a hit, the CPU can really execute one instruction per CPU cycle. In order to keep the caches consistent and arbitrate between the memory accesses of the two caches, we introduce a control circuit. This circuit also decides whether a given request accesses the instruction cache, the data cache or the main memory. Figure 1.5 depicts this situation.

A cache memory interface has to fulfill the correctness criterion supplied in definition 1.5.2. Thus, a cache memory interface is transparent in the sense that the CPU does not really have to know anything about the implementation of the memory interface, be it simple or with split caches.

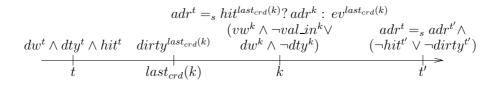

Similar to definition 1.5.2 of correct memory interface, we introduce the notion of consistent caches in this section. As outlined in the previous sections, caches signal valid data with an active hit signal. Hence, a straightforward cache consistency property states that in cases of a hit, the cache returns the same data a consistent memory would—namely, the data that was last written to the read address. Table 1.2 summarizes all cache input and output signals in order to allow for a formal definition of cache consistency. Note that we currently only refer to adr, din, dout, and cdwb; all the

other signals are introduced in chapter 2.

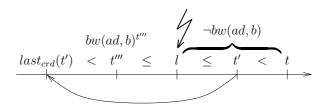

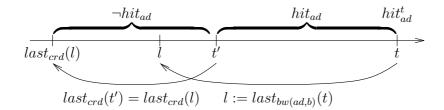

**Definition 1.5.3** For any  $ad \in \mathbb{B}^a$  and b < B, we introduce a parameterized predicate on the cache input that captures writes to byte b of address ad by defining  $\$.bw(ad,b) := (adr = ad) \land cdwb[b]$ .

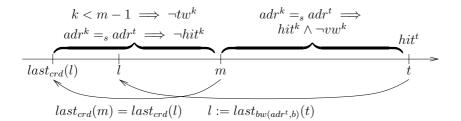

A cache is called **consistent** iff the following properties hold for any cycle  $t \in \mathbb{N}^+$  and any  $b \in \mathbb{Z}_B$ :

$$hit^{t} \implies \exists_{\$.bw(adr^{t},b)}^{last}(t) \wedge last_{\$.bw(adr^{t},b)}(t) > 0 \wedge |dout^{t}|_{b} = \left| din^{last_{\$.bw(adr^{t},b)}(t)} \right|_{b}$$

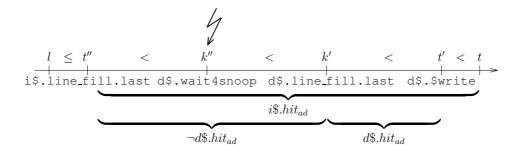

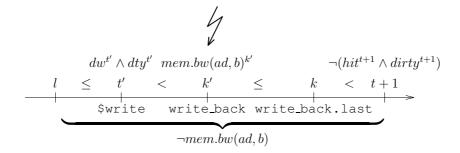

In the following chapter, we will show different cache implementations to fulfill the above cache consistency property and some other additional properties. In chapter 3, we then use abstract instruction- and data caches obeying the above definition in order to implement a cache memory interface and prove it correct according to definition 1.5.2. Finally, chapter 4 only uses the definition of a correct memory interface in order to prove a whole CPU correct. Thanks to clean interfaces, putting these three proofs together to a single proof of the overall correctness of a pipelined out-of order CPU with a cache memory interface comprising split instruction- and data caches does not require any additional proof effort.

# Chapter 2

## Caches

In this chapter we will establish implementations and correctness proofs for different implementations of caches. Since we exclusively deal with caches in this chapter, we will use the shorthand notation bw(ad,b) for bw(ad,b) that was introduced in definition 1.5.3 in the previous chapter.

### 2.1 Definition

A cache is a small memory containing a subset of the data of the main memory. The basic idea is that an access to this small cache memory is fast as opposed to the slow off-chip main memory. The cache signals that it holds valid data for an address adr by raising a hit signal. If, on the other hand, the cache produces a miss, i.e., it does not raise the hit signal, an access to the main memory is required. The required data is read from the main memory and stored in the cache. This is done due to the heuristic principle of  $temporal\ locality$ : If a CPU accesses an address adr, it is likely that it accesses the same memory location adr once again later on. By copying this data to the cache, a future access to the same address thus becomes fast.

If the CPU accesses an address adr, it is also likely that it accesses an address close to adr later on, i.e., adr+1. This is called the *principle of spatial locality*. Therefore, on a miss, not only one word is read from the main memory and stored in the cache, but a whole so-called  $cache\ line$ . A cache line consists of  $2^s$  data words, where  $s \in \mathbb{N}$  is a cache parameter. Note that data words are called  $cache\ sectors$  in [MP00]. The transfer of a cache line from the main memory to the cache is called a  $line\ fill$ . For s=0, a cache line just equals one word. For s>0, the cache line consists of multiple data words and we call the cache sectored. One further reason for the use of sectored caches is the fact that usually, the main memory consists of dynamic RAM which allows for fast accesses to consecutive addresses called bursts.

In case of a cache miss, it is possible that the cache is full, i.e., all the cache memory contains only valid data and the cache cannot hold the additional

Figure 2.1: Partitioning of an a-bit cache address

cache line that is to be added in a line fill. In this case, some valid cache line has to be evicted from the cache in order to make room for the new cache line. We perform this eviction in two steps, i.e., we first invalidate the 'old' cache line and only then perform a line fill for the new cache line. The process of selecting an appropriate cache line for invalidation is called replacement policy. Different replacement policies are described later on.

An important aspect in designing caches is the mapping of memory locations to possible cache locations. In general, a memory location is mapped to a set of cache locations that can hold the data of the corresponding memory location. In case of software caches, any memory location usually can be mapped to any cache location. This is called *full associativity*. In a hardware implementation of a cache, however, full associativity is too expensive except for very small caches, e.g., caches with less than 64 entries that are used for translation look-aside buffers (TLBs).

In common hardware caches, memory locations are mapped to sets of cache locations that all have the same cardinality. We therefore introduce an additional cache parameter K equaling this cardinality. We distinguish three types of caches according to the value of K. In the most simple case, K=1, we call the cache direct mapped. For  $K\geq 2$ , the cache is called K-way set associative; it basically consists of K so-called ways which are direct mapped caches themselves. If K equals the number of cache lines the cache memory can hold, the cache is actually fully associative.

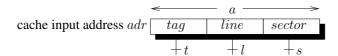

In order to specify the size of the cache data memory, we introduce a cache parameter l such that a single cache way can hold  $2^l$  different cache lines. This equals a total of  $K \cdot 2^{l+s}$  words since a cache line consists of  $2^s$  words and the cache consists of K ways. Additionally, we set t := a - l - s. A cache input address adr is split into the three parts tag, line, and sector according to figure 2.1. Two memory addresses that only differ in their tag part are mapped to the same set of K cache locations. Any two addresses differing only in the sector part belong to the same cache line, thus offering the specified line size of  $2^s$  data words.

**Definition 2.1.1** Let  $n \in \mathbb{N}^+$  and  $i, j \in \mathbb{Z}_n$  with i > j. We then introduce for any  $a, b \in \mathbb{B}^n$  the following shorthand notations:

$$\begin{array}{ll} a =_j^i b & :\iff & a[i-1:j] = b[i-1:j] \\ a =_j b & :\iff & a =_j^n b \\ [a]_j & := & \{a' \in \mathbb{B}^n | a =_j a'\} \end{array}$$

| Parameter | Meaning                                      |

|-----------|----------------------------------------------|

| В         | number of bytes in a data word               |

| a         | address width of the memory, $a = t + l + s$ |